实验四QPSK与DQPSK调制实验.docx

实验四QPSK与DQPSK调制实验.docx

- 文档编号:14762463

- 上传时间:2023-06-27

- 格式:DOCX

- 页数:8

- 大小:202.44KB

实验四QPSK与DQPSK调制实验.docx

《实验四QPSK与DQPSK调制实验.docx》由会员分享,可在线阅读,更多相关《实验四QPSK与DQPSK调制实验.docx(8页珍藏版)》请在冰点文库上搜索。

实验四QPSK与DQPSK调制实验

一、实验目的

在2PSK,2DPSK的学习基础上,掌握QPSK,以及以其为基础的DQPSK,OQPSK,/4—DQPSK等若干种相关的重要调制方式的原理,从而对多进制调相有一定了解。

二、实验设备

1、“移动通信技术应用综合实训系统”实验仪一台。

2、50MHz示波器一台。

3、实验模块:

信源模块,QPSK-调制模块。

三、实验原理

一)基本理论

(A)四相绝对移相键控(QPSK)的调制

四相绝对移相键控利用载波的四种不同相位来表征数字信息。

由于每一种载波相位代表两个比特信息,故每个四进制码元又被称为双比特码元。

我们把组成双比特码元的前一信息比特用a代表,后一信息比特用b代表。

双比特码元中两个信息比特ab通常是按格雷码(即反射码)排列的,它与载波相位的关系如表所列。

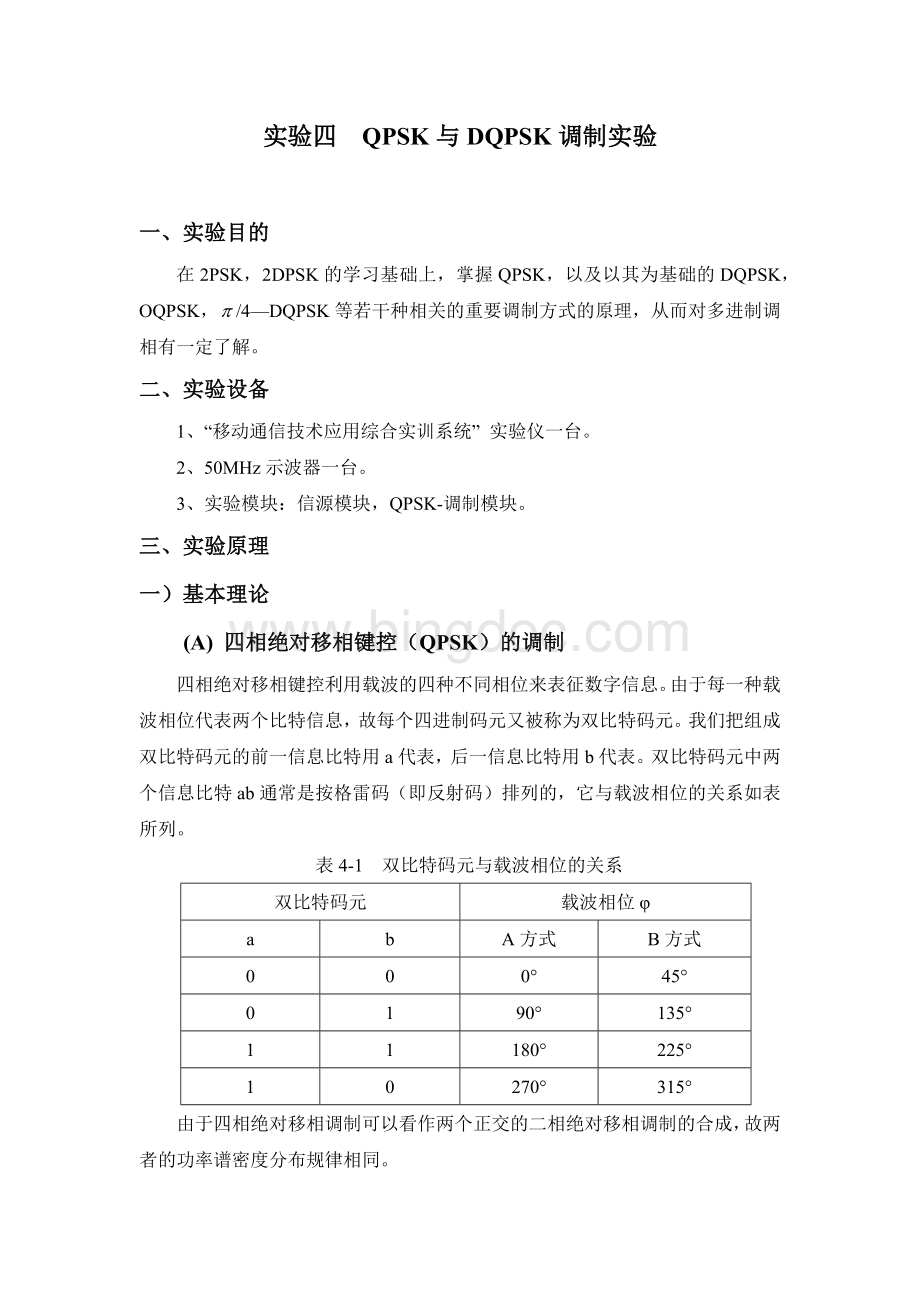

表4-1双比特码元与载波相位的关系

双比特码元

载波相位φ

a

b

A方式

B方式

0

0

0°

45°

0

1

90°

135°

1

1

180°

225°

1

0

270°

315°

由于四相绝对移相调制可以看作两个正交的二相绝对移相调制的合成,故两者的功率谱密度分布规律相同。

下面我们来讨论QPSK信号的产生与解调。

QPSK信号的产生方法与2PSK信号一样,也可以分为调相法和相位选择法。

(1)调相法

用调相法产生QPSK信号的组成方框图如下所示。

图4-1QPSK信号的组成方框图

设两个序列中的二进制数字分别为a和b,每一对ab称为一个双比特码元。

并设经过串并变换后上支路为a,下支路为b。

双极性的a和b脉冲通过两个平衡调制器分别对同相载波及正交载波进行二相调制。

表4-2QPSK信号相位编码逻辑关系

a

1

0

0

1

b

1°

1°

0°

0°

A路平衡调制器输出

0°

180°

180°

0°

B路平衡调制器输出

270°

270°

90°

90°

合成相位

315°

225°

135°

45°

(2)相位选择法

用相位选择法产生QPSK信号的组成方框图如下所示。

图4-2相位选择法产生QPSK信号方框图

(B)四相相对移相键控(DQPSK)的调制

所谓四相相对移相键控也是利用前后码元之间的相对相位变化来表示数字信息。

若以前一码元相位作为参考,并令△φ为本码元与前一码元的初相差。

,则信息编码与载波相位变化仍可用QPSK信号相位编码逻辑关系表来表示。

不过,φ应变为△φ。

对于DQPSK而言,可先将输入的双比特码经码型变换,再用码型变换器输出的双比特码进行四相绝对移相,则所得到的输出信号便是四相相对移相信号。

通常采用的方法是码变换加调相法和码变换加相位选择法。

(1)码变换加调相法

码变换加调相法产生DQPSK原理图与调相法产生QPSK原理图相比,仅在串/并变换后多了一个码变换器。

表4-3DQPSK信号相位编码逻辑关系

双比特码元

载波相位变化

△φ

a

b

0

0

0°

0

1

90°

1

1

180°

1

0

270°

表4-4四相相对调相码变换的逻辑功能

本时刻到达的ab及所要求的相对相位变化

前一码元的状态

本时刻应出现的码元状态

ab

△φ

cd

θ

cd

θ

00

0°

00

135°

00

135°

01

225°

01

225°

11

315°

11

315°

10

45°

10

45°

01

90°

00

135°

00

225°

01

225°

01

315°

11

315°

11

45°

10

45°

10

135°

11

180°

00

135°

00

315°

01

225°

01

45°

11

315°

11

135°

10

45°

10

225°

10

270°

00

135°

00

45°

01

225°

01

135°

11

315°

11

225°

10

45°

10

315°

(2)码变换加相位选择法

码变换加相位选择法产生DQPSK信号的原理十分简单,它的组成方框图如下所示。

图4-3码变换加相位选择法产生DQPSK信号方框图

经分析,它与相位选择法产生QPSK信号的组成方框图完全相同。

不过,这里逻辑选相电路除按规定完成选择载波的相位外,还应实现将绝对码转换成相对码的功能。

也就是说,在四相绝对移相时,直接用输入双比特码去选择载波的相位;而在四相相对移相时,需要将输入的双比特码ab转换成相应的双比特码cd,再用cd去选择载波的相位。

这样,便可产生QDPSK信号。

(C)OQPSK的调制

OQPSK和QPSK调制类似,不同之处是在正交支路引入了一个比特(半个码元)的延迟,这使得两个支路的数据不会同时发生变化,因而不可能像QPSK那样产生±的相位跳变,而仅产生±/2的相位跳变。

因此,OQPSK频谱旁瓣要低于QPSK信号的旁瓣。

图4-4QPSK的星座图和相位转移图

图4-5OQPSK的星座图和相位转移图

(D)/4—DQPSK的调制

/4-DQPSK是对QPSK信号特性进行改进的一种调制方式,改进之一是将QPSK的最大相位跳变±,降为±3/4,从而改善了/4-DQPSK的频谱特性.改进之二是解调方式,QPSK只能用相干解调,而/4-DQPSK既可用相干解调,也可用非相干解调.

/4-DQPSK的原理框图如下所示.输入数据经串/并变换后上下支路分别为SI,SQ,再经差分相位编码后上下支路分别为UK,VK。

图4-6/4-DQPSK信号的产生原理框图

设已调信号Sk(t)=cos(ωct+Φk)

式中,θ为kT≤t≤(k+1)T之间的附加相位.上式可展开成

Sk(t)=cosωctcosΦk-sinωctsinΦk

当前码元的附加相位θ是前一码元附加相位φ与当前码元相位跳变量△φ之和,即Φk=Φk-1+△Φk

Uk=cosΦk=cos(Φk-1+△Φk)=cosΦk-1·cos△Φk-sinΦk-1·sin△Φk

Vk=sinΦk=sin(Φk-1+△Φk)=sinΦk-1·cos△Φk+cosΦk-1·sin△Φk

其中,sinΦk-1=Vk-1,cosΦk-1=Uk-1,上面两式可以改写为

Uk=Uk-1·cos△Φk-Vk-1·sin△Φk

Vk=Vk-1·cos△Φk+Uk-1·sin△Φk

这是/4-DQPSK的一个基本关系式.它表明了前一码元两个正交信号Uk-1、Vk-1与当前码元两正交信号Uk、Vk之间的关系.它取决于当前码元的相位跳变量△Φk,而当前码元的相位跳变量△Φk则又取决于差分相位编码器的输入码组SI、SQ,他们的关系如下表所示.

表4-5/4-DQPSK的相位跳变规则

SI

SQ

△Φk

cos△Φk

sin△Φk

1

1

/4

1/

1/

-1

1

3/4

-1/

1/

-1

-1

-3/4

-1/

-1/

1

-1

-/4

1/

-1/

上述规则决定了在码元转换时刻的相位跳变量只有±/4和±3/4四种取值.U和V只可能有0,±1/,±1五种取值.

设该滤波器的矩形脉冲响应函数为,那么最后形成的∏/4-DQPSK信号可以表示为

S(t)=g(t-kTs)cosΦkcosωct-g(t-kTs)sinΦksinωct

二)测试点

QPSK调制模块上各个输入输出点与与测试点的意义:

BS_IN:

QPSK_调制模块上外同步时钟信号的输入点。

BS_OUT:

QPSK_调制模块自身产生同步时钟信号的输出测试点。

NRZ_IN:

QPSK调制模块的基带数字信号。

QPSK:

对基带数字信号调制所产生的QPSK连续频带信号。

TEST_CAR:

载波测试点。

TEST_I:

QPSK调制的一条支路信号测试点。

TEST_Q:

QPSK调制的另一条支路信号测试点。

TEST_BI:

DQPSK调制的一条支路信号测试点。

TEST_BQ:

DQPSK调制的一条支路信号测试点。

QPSK_调制模块面板上各个跳线帽的意义:

BS选择:

上方BS_IN表示引入外同步时钟信号,

下方BS_OUT表示QPSK_调制模块自身产生同步时钟信号。

BS_OUT频率:

上方32K表示QPSK_调制模块自身产生同步时钟信号频率为32KHz,下方64K表示QPSK调制模块自身产生同步时钟信号频率为64KHz。

载波频率:

上方32K表示QPSK的调制频率为32KHz,下方1.024M表示QPSK的调制频率为32KHz。

调制模式:

上方绝对表示QPSK调制,下方相对表示QDPSK调制。

初始相位:

上方0度表示采用00,900,1800,2700方案,下方45度表示采用450,1350,2250,3150方案。

左上方跳线帽则表示是否选择EPC2存储器来存储FPGA程。

置于左边表示采用EPC2存储器来存储FPGA程序,使得断电后程序不丢失。

置于右边表示程序直接存放在FPGA芯片中,断电后程序将会丢失。

四、实验步骤

1、关闭实验仪上的交流电源开关。

2、将QPSK-调制模块的BS选择跳线帽置于下方BS-OUT位置使QPSK-调制模块自身输出同步信号,再将SOURCE模块右边的跳线帽置于下方使A_OUT输出数字基带信号。

3、将SOURCE的A-OUT与QPSK-调制模块的NRZ-IN连接起来。

打开电源开关与各个实验模块开关,观察并记录QPSK处的波形。

3、分别改变BS-OUT频率,载波频率,初始相位,绝对相对,重做该实验,并相互比较。

4、改变信源信号,重复上述实验步骤。

五、实验报告

1、简述QPSK调制原理。

2、观察以上各种情况下的各信源信号波形与位同步信号波形以及最终的QPSK、DQPSK调制波形,并与原理对比分析说明。

3、试比较在其他参数都相同时,32K与1.024M不同的载波频率下调制信号波形的不同之处并说明原因。

4、画出原始基带信号与根据文中所提供的原理与芯片资料,试用VHDL或VerilogHDL语言重新编程实现OQPSK,/4—DQPSK的调制(选做)。

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 实验 QPSK DQPSK 调制

冰点文库所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰点文库所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

“安全培训随机抽查”管理制度.doc

“安全培训随机抽查”管理制度.doc

“代位求偿”案件索赔申请书(责任对方为机动车方)【范文】.xls

“代位求偿”案件索赔申请书(责任对方为机动车方)【范文】.xls