基于FPGA的DDS波形发生器.docx

基于FPGA的DDS波形发生器.docx

- 文档编号:160129

- 上传时间:2023-04-28

- 格式:DOCX

- 页数:17

- 大小:937.65KB

基于FPGA的DDS波形发生器.docx

《基于FPGA的DDS波形发生器.docx》由会员分享,可在线阅读,更多相关《基于FPGA的DDS波形发生器.docx(17页珍藏版)》请在冰点文库上搜索。

基于FPGA的DDS波形发生器

基

于

FPGA

的

DDS

波

形

发

生

器

设

计

班级:

08电子信息

姓名:

焦春焕

学号:

080230159

基于FPGA的DDS波形发生器设计

【摘要】

详细阐述了直接数字频率合成器的原理与设计,利用Verilog

HDL语言实现了DDS功能。

【概述】将现场可编程逻辑器件FPGA

和DDS技术相结合,具体的体现

了基于VHDL语言的灵活设计和修改方式是对传统频率合成实现方法的一次重要改进。

FPGA器件作为系统控制的核心,其灵活的现场可更改性,可再配置能力,对系统的各种改进非常方便,在不更改硬件设计部分电路的基础上还可以进一步提高系统的性能。

文章给出仿真结果,经过验证本设计能够达到其预期性能指标。

【系统设计部分】

·1整个设计组织结构

DDS基本原理

DDS建立在采样定理基础上,首先对需要产生的波形进行采样,将采样值数字化后存入存储器作为查找表,然后通过查表读取数据,再经D/A转换器转换为模拟量,将保存的波形重新合成出来。

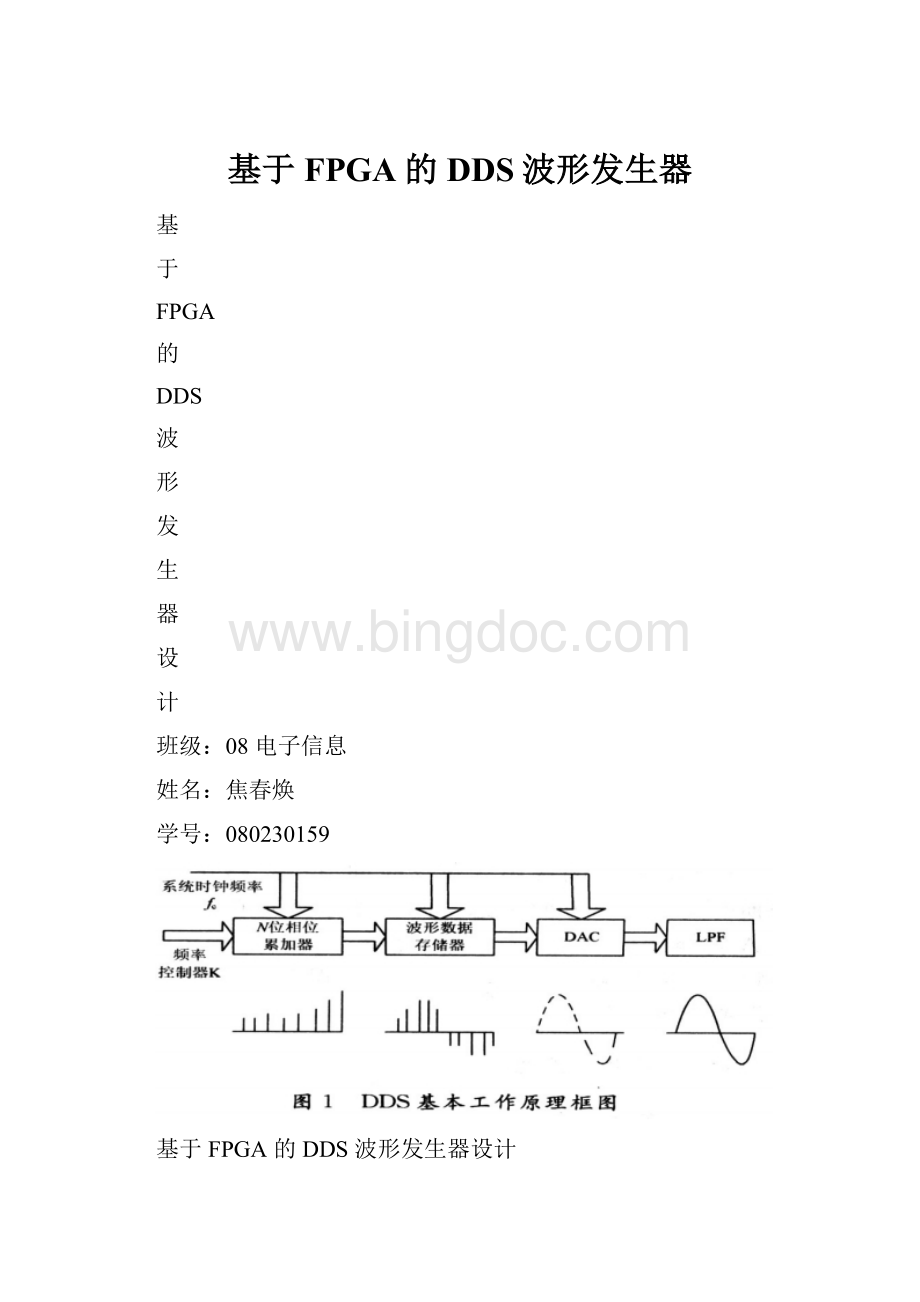

DDS基本原理框图如图1所示。

除了滤波器(LPF)之外,DDS系统都是通过数字集成电路实现的,易于集成和小型化。

系统的参考时钟源通常是一个具有高稳定性的晶体振荡器,为各组成部分提供同步时钟。

频率控制字(FSW)实际上是相位增量值(二进制编码)作为相位累加器的累加值。

相位累加器在每一个参考时钟脉冲输入时,累加一次频率字,其输出相应增加一个步长的相位增量。

由于相位累加器的输出连接在波形存储器(ROM)的地址线上,因此其输出的改变就相当于查表。

这样就可以通过查表把存储在波形存储器内的波形抽样值(二进制编码)查找出来。

ROM的输出送到D/A转换器,经D/A转换器转换成模拟量输出。

系统总体方案设计

该设计以FPGA开发平台为核心,将各波形的幅值/相位量化数据存储在ROM内,按照设定频率,以相应频率控制字k为步进,对相位进行累加,以累加相位值作为地址码读取存放在存储器内的波形数据,经D/A转换和幅度控制、滤波即可得到所需波形。

波形发生器采取全数字化结构,用硬件描述语言Verilog设计实现其频率可调可显示。

经开发平台的D/A转化和外加滤波整形处理波形数据,理论上能够实现任意频率的各种波形。

系统总体设计方框图如图2所示。

·2系统功能各个子单元设计实现

(1)波形数据产生单元

波形数据产生单元是信号发生器设计的主体。

在此,采用DDS原理设计的信号发生器能完成三种波形(正弦、三角和方波)数据的产生,而且根据控制信号还可完成选定波形指定频率的输出。

波形数据产生单元按功能实现上的相互联系可划分为频率控制字生成模块、相位累加器模块和波形数据ROM表模块,如图3所示。

其中,频率控制字生成模块可根据输入产生指定频率字,同时显示输入频率数字。

相位累加器模块负责对所选波形的相位寻址,以频率控制字作为步长反复进行累加运算。

波形数据ROM表模块存放三种波形的幅值/相位量化值,通过地址选择相应波形的数据。

系统输入控制使用4×4键盘.键盘主要按键功能介绍如下:

“0~9”:

数字键,设定信号频率;

“确定”:

用于对波形信号设置的确认,波形信号的设置必须“确定”后才有效;

“←”:

删除已输入信号频率数字的最后一位,用于修改设置的频率;

“清零”:

将频率数字快速全部清零;

“↑”:

步进增大控制;

“↓”:

步进减小控制。

设定频率输出范围为1kHz~10MHz,频率步进为50Hz。

系统输出采用8个LED数码管,以扫描方式显示(单位为Hz)频率数字。

根据DDS原理,以步进值50Hz作为频率控制字1,那么最大值10MHz对应的频率控制字为200000,用18位二进制数值就可以表示(218>200000)。

从抽样值恢复出原波形数据,理论上每个周期波形数据至少抽取2个点,考虑到实际应用时受频率损耗、线间串扰等因素的限制,该设计采用22b的频率控制字和相位累加器,4Kb的8位波形ROM表,取相位累加器输出的高12b寻址波形数据,三种波形按幅值/相位对应关系分别存储782个数据。

故各波形数据单位周期有800768(782×210)个相位状态,完全满足任一波形在单位周期内取4个幅值点的要求,可保证即使输出最大频率的波形仍能达到较好的效果。

波形选择功能由两位开关组合实现,共有四种状态,其中三组用来表征不同的波型,另一组留作扩展波形用。

(2)D/A转换单元

数/模转换单元是继波形数据产生单元之后,将数字量形式的波形幅值转换成所要求的合成频率的模拟量形式信号。

DAC输出信号实际上是阶梯模拟信号,需在数/模转换后利用低通滤波器对波形进行平滑处理。

在此,采用ADI公司生产的单片双8位CMOS乘法数/模转换器AD7528,线性度达到1/2,转换时间达到纳秒级,可以很准确地进行10MHz信号的量化运算。

(3)滤波处理单元

滤波器是一种能通过有用频率信号而同时抑制(或衰减)无用频率信号的电子装置。

由于运算放大器具有近似理想的特性,且可以省去电感,得到接近理论预测的频率响应特性。

构成有源滤波电路后还具有一定的电压放大和缓冲作用,并能减小体积。

综合考虑,系统采用运算放大器SL560构成二阶低通滤波器。

·3各个子单元之间的接口关系

硬件系统设计硬件系统由4部分组成:

必要的外围电路用于频率控制、以FPGA为控制核心的处理系统用于DDS信号发生、DAC模块用于数模转换,滤波器用于对模拟输出进行平滑和去噪,其中FPGA模块又由串口接收模块,双口RAM模块以及DDS模块组成。

硬件系统实现框图如图4所示。

由于DAC模块和滤波模块电路简单,容易实现,本文不予以详细叙述,仅给出FPGA核心电路设计。

(1)DDS

模块设计DDS

模块由三个底层模块组成:

相位累加器(ADDER26B)、寄存器

(REG26B)和波形数据存储器(sin_rom)。

各模块之间的联系可以从DDS模块顶层实体图(图5)中看出。

ADDER26B为波形发生器的相位控制器;REG26B为相位寄存器,起到数据缓冲的作用;sin_rom为波形数据存储器,用于存储串口接收到的波形数据。

(2)波形存储模块该模块是使用MegaWizardPlug-InManager定制的宏功能模块,用来存储一个周期的波形数据。

本设计定制的双口RAM控制模块具有读写两个端口,通过两路时钟和两套地址系统,对RAM进行操作:

串口模块对RAM进行写操作,更新波形数据;DDS模块对RAM进行读取操作,产生阶梯序列。

(3)串口模块串口模块用Verilog语言编写,用于接收上位机发送的波形数据,同时配合双口RAM控制器将数据存储到嵌入在FPGA内部的双口RAM内。

数据帧格式为:

1位起始位,8位数据位,1位停止位。

为串口模块顶层符号图。

·4该设计与其它设计关系

DDS

系统中的参考时钟通常是一个高稳定性的晶体振荡器,用来作为系统时钟同步整个系

统的各组成部分。

频率控制字(FSW-FrequeencySettingWord)实际就是相位增量值,用来做

相位累加器的累加值。

相位累加器在每一个参考时钟脉冲输入时,

把频率字累加一次,其输

出相应地增加一个步长的相位增量,由于相位累加器的输出连接在波形存储器地址线上,

因

此其输出的改变就相当于进行查表。

这样就可把存储在波形存储器内的波形采样值经过查表查出,输出到D/A转换器。

在系统时钟脉冲的作用下,相位累加器不停地累加,也即不停

地查表,不停地把波形数据送到D/A转换器转换成模拟量输出,

从而合成波形输出。

滤波器

则进一步平滑D/A转换器输出的近似所需波型的锯齿阶梯波,同时滤除不必要的杂波。

同时由于相位累加器字长的限制,相位累加器累加到一定数值后,其输出将会溢出,产生的波形存储器的地址数值就会循环一次,意味着输出的波形完成了一个周期。

所以改变频率控制字,就可以改变累加器的循环频率,在时钟频率不变的情况下就可以改变输出率[3]。

【仿真综合部分】

·1关键节点部分位置,作用及其测试波形描述

频率控制字的生成直接影响着波形数据的寻址,该模块负责快速记录并实时显示输入的频率数字,准确计算得到相应的频率控制字。

系统键盘为高速动态扫描(频率为200Hz),采用状态机设计,设置了按键去抖动功能。

在FPGA开发平台对该模块进行功能验证,整体无误操作产生,几乎没有时滞效应,按键的防抖动效果也良好,达到了预期的目的。

本设计多次用到寄存器,D32、D32CO、它们大概原理相同,但有些细小的差别。

本质都是一个32位的D触发器,在一个上升沿到来时开始存储。

用VHDL设计32位的触发器,其模块如图3.4所示

仿真与分析:

D32系列触发器仿真波形如图5、6所示

图5D32仿真波形

图6D322CO仿真波形

本设计采用L=32,N=8。

正弦ROM查找表完成fsin(B)的查表转换,也可以理解成相位到

幅度的转换,它的输入是相位累加器的输出,事实上就是ROM的地址值;输出送往D/A,转化成模拟信号。

用VHDL设计8位ROM,其模块如图7所示

正弦波ROM仿真如图8所示

图8

正弦波仿真波形

·2I/O引脚名称,作用及其测试波形描述

DAC0832引脚及其功能

图9中,当ILE为高电平,片选信号/CS和写信号/WR1为

低电平时,输入寄存器控制信号为1,这种情况下,输入寄存器的

输出随输入而变化。

此后,当/WR1由低电平变高时,控制信号

成为低电平,此时,数据被锁存到

输入寄存器中,这样输入寄存器的输出端不再随外部数据DB的变化而变化。

对第二级锁存来说,传送控制信号/XFER和写信号/WR2

图9DAC0832引脚图

同时为低电平时,二级锁存控制

信号为高电平,8位的DAC寄存器的输出随输入而变化,此后,当/WR2由低电平变高时,控制信号变为低电平,于是将输入寄存器的信息锁存到DAC寄存器中。

图9中其余各引脚的功能定义如下:

(1)、DI

7

~DI

0

:

8位的数据输入端,DI

7

为最高位。

(2)、I

OUT1

:

模拟电流输出端1,当DAC寄存器中数据全为1时,输出电流最大,当

DAC寄存器中数据全为0时,输出电流为0。

(3)、I

OUT2

:

模拟电流输出端2,I

OUT2

与I

OUT1

的和为一个常数,即I

OUT1

+I

OUT2

=常数。

(4)、R

FB

:

反馈电阻引出端,DAC0832内部已经有反馈电阻,所以RFB

端可以直接接到

外部运算放大器的输出端,这样相当于将一个反馈电阻接在运算放大器的输出端和输入端之间。

(5)、V

REF

:

参考电压输入端,此端可接一个正电压,也可接一个负电压,它决定0至255

的数字量转化出来的模拟量电压值的幅度,V

REF

范围为(+10~-10)V。

V

REF

端与

D/A内部T形电阻网络相连。

(6)、Vcc:

芯片供电电压,范围为(+5~15)V。

(7)、AGND:

模拟量地,即模拟电路接地端。

(8)、DGND:

数字量地。

图10DAC0832内部结构图

·3采用的pld器件型号

·4

片篇内各种资源的使用情况

与下位机通信本设计通过串行通信实现PC机与硬件系统间的数据传输。

串口通信遵循固定

的协议,PC

端软件和硬件系统都需要对串口通信模块进行设置,保证通信双方采用相同的

波特率。

当串口对象和硬件设备连接成功,就可以收发数据。

硬件系统设计硬件系统由4部分组成:

必要的外围电路用于频率控制、以FPGA为控制核心的处理系统用于DDS信号发生、DAC模块用于数模转换,滤波器用于对模拟输出进行平滑和去噪,其中FPGA模块又由串口接收模块,双口RAM模块以及DDS模块组成。

由于DAC模块和滤波模块电路简单,容易实现,本文不予以详细叙述,仅给出FPGA核心电路设计。

【结论】

DDS的总体

其低层原理图见附录,下面介绍DDS的总体。

(1)模块图

图11DDS模块图

仿真与分析:

1200KHZ正弦波仿真波形如图12所示;

10KHZ正弦波仿真波形如图13所示;

图121200KHZ正弦波仿真波形

图1310KHZ正弦波仿真波形

在完成设计并编译工程后,建立SignalTapII(.stp)文件并加入工程、配置STP文件、编译并下载设计到FPGA,在QuartusII软件中显示被测信号的波形如下图所示。

正弦波

方波

三角波

锯齿波

图12、图13是两组正弦波的输出信号。

其输出频率与频率控制字送来数据对应起来,仿真波形正常。

从上述两组波形可以看出,对应的频率控制字输出对应的频率,其幅值与来自频率控制控制的相位相对应。

输出的幅值与ROM中的数字相对应,其DDS的主体已基本达到设计要求。

介绍了以直接数字频率合成技术(DDS)为基础的波形信号发生器工作原理和设计过程,并在FPGA实验平台上设计实现了满足各功能指标的信号发生器。

系统硬件除需外加滤波整形电路外,其余部分均可在FPGA开发实验系统KH-310上集成开发,系统软件可在Quartus下编写代码,实现数据信息处理和控制操作等功能。

整体开发环境成熟,应用工具齐全,随着FPGA性价比的不断提高,基于FPGA平台开发信号发生器将逐步走向标准化、规模化和产品化。

现代电子和通信技术的发展,对信号发生器提出了更高、更严格的要求。

除了对信号频率范围、带宽和频率分辨率的严格限制外,对信号的波型及调制特性等也有着苛刻的规定。

研究和开发具有更高性价比的信号发生器将是当前和今后一段时间内亟需解决的课题。

这里旨在建立一种基于FPGA的简单数字信号发生器设计方法。

若能充分利用FPGA强大的数据运算处理能力以及编程灵活、运

行速率快等优点,合理整合IP核资源和SoPC技术,简化设计结构,一定可以设计出功能多样、性能更加出色的信号发生器。

【附录】

moduleDDS(CLK,K,Rst,Out);

inputCLK;

input[7:

0]K;

inputRst;

output[7:

0]Out,

wire[19:

0]Temp,Temp;

AdderU1(.CLK(CLK),Rst(Rst),K(K),SignalOut(Temp1));

RegU2(.CLK(CLK),.Rst(Rst),.Datain(Temp1),Dataout(Temp2));

Sin_RomU3(.address(Temp2[11:

4]),.clock(CLK),.q(Out));

//FangBo_RomU3(.address(Temp2[11:

4]),.clock(CLK),.q(Out));方波

//SawtoothU3(.address(Temp2[11:

4]),.clock(CLK),.q(Out));锯齿波

//Tri_RomU4(.address(Temp2[11:

4]),.clock(CLK),.q(Out));三角波

endmodule

相位累加器模块:

moduleAdder(CLK,RsOut);

inputCLK;

inputRst;

input[7:

0]K;

output[19:

0

reg[19:

0]SignaOut;

always@(posedgeCLKornegedgeRst)

begin

if(!

Rst)

SignalOut<=0:

else

SignalOut<=Signal+K;

end

endmodule

寄存器模块

moduleReg(CLK,Datain,Dataout);

inputCLK;

inputRst;

input[19:

0]Datain;

output[19:

0]Dataout

reg[19:

0]Dataout;

always@(posedgeCLKornegedgeRst)begin

if(!

Rst)

Dataout<=0:

else

Dataout<=Datain;

end

endmodule

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 基于 FPGA DDS 波形 发生器

冰点文库所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰点文库所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

整编新型生态农业旅游休闲农庄项目发展建设市场研究报告.docx

整编新型生态农业旅游休闲农庄项目发展建设市场研究报告.docx