FM8PS53中文版.docx

FM8PS53中文版.docx

- 文档编号:17691171

- 上传时间:2023-08-03

- 格式:DOCX

- 页数:82

- 大小:375.85KB

FM8PS53中文版.docx

《FM8PS53中文版.docx》由会员分享,可在线阅读,更多相关《FM8PS53中文版.docx(82页珍藏版)》请在冰点文库上搜索。

FM8PS53中文版

EPROM/ROM-Based8-BitMicrocontrollerSeries

这片说明文档以下两种型号MCU

∙FM8PS53E:

EPROMdevice(OPT)

∙FM8PS53:

MaskROMdevice(掩膜)

功能特性

∙只有42个单字指令

∙除分支指令为两个周期指令以外其余为单周期指令

∙PC寻址范围为13-bit

∙GOTO指令能跳转到所有的ROM/EPROM地址空间

∙子程序能返回到所有的ROM/EPROM地址空间

∙能处理8位数据

∙5级硬件堆栈

∙运行速度:

DC-20MHz工作频率

DC-100ns指令周期

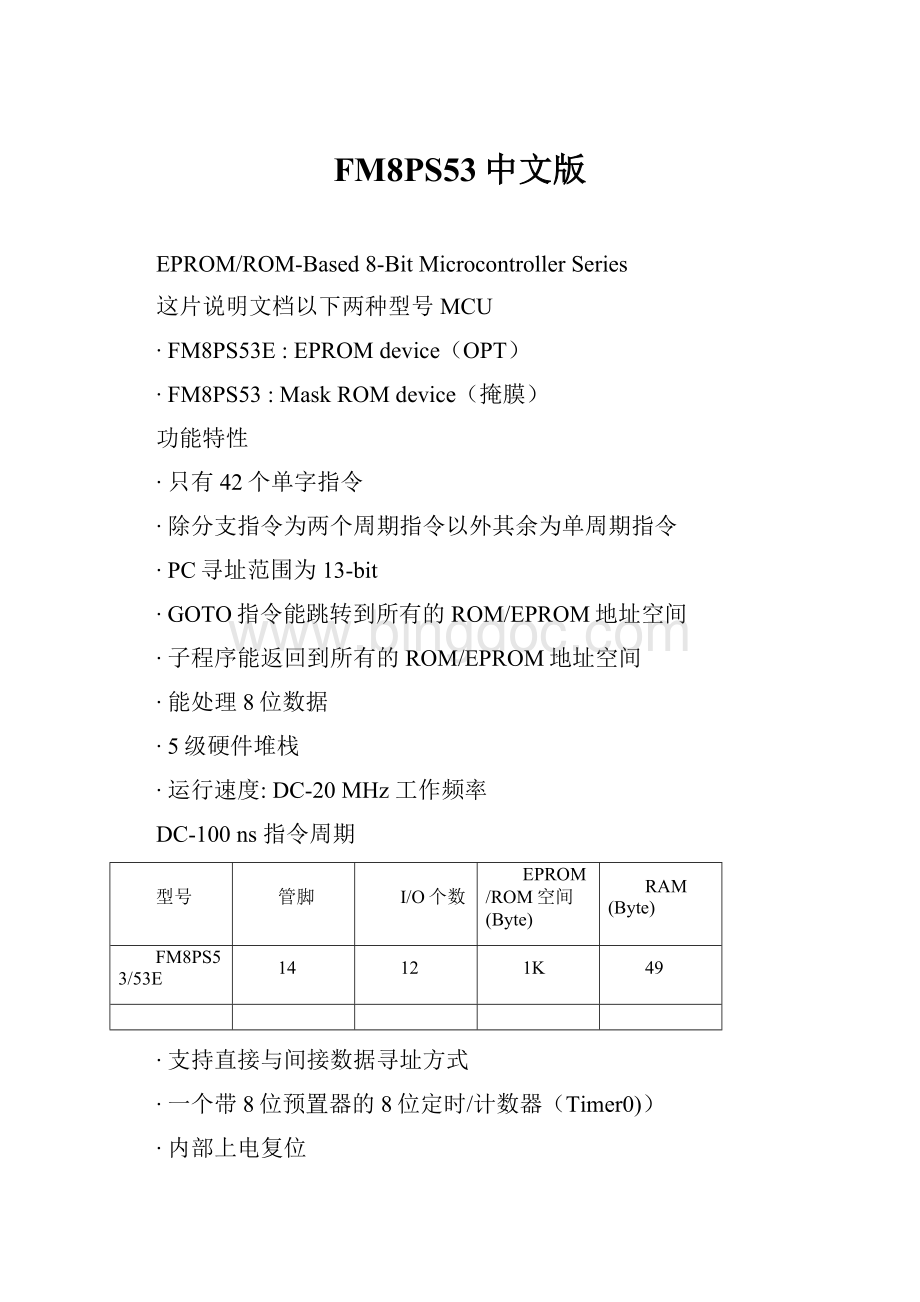

型号

管脚

I/O个数

EPROM/ROM空间(Byte)

RAM(Byte)

FM8PS53/53E

14

12

1K

49

∙支持直接与间接数据寻址方式

∙一个带8位预置器的8位定时/计数器(Timer0))

∙内部上电复位

∙内含一个低电压检测电路供掉电复位使用

∙上电复位计数器(PWRT)和振荡启动计数器(OscillatorStart-upTimerOST)

∙内部振荡器集成了一个看门狗保证了可靠的操作同时软件使能看门狗操作

∙两类双向输入输出I/O口IOA和IOB

∙通过编程控制I/O端口的上拉/下拉、开路等状态

∙一个内部计数中断源;两个外部中断源:

INT管脚,PortB的输入改变

∙通过INT管脚或者PortB的输入改变来实现睡眠唤醒

∙省电睡眠模式

∙内部有8MHz,4MHz,1MHz,和455KHzRC振荡器

∙有可靠的保证使得程序代码不被读出。

∙内部RC振荡器

∙提供以下振荡源的选择:

-ERC:

ExternalResistor/CapacitorOscillator(外部的RC振荡器)

-IRC/ERIC:

InternalorExternalResistor/InternalCapacitorOscillator–(内部电阻内部的电容RC振荡器或外部的电阻内部的电容RC振荡器)

HF:

HighFrequencyCrystal/ResonatorOscillator(高频率的晶体协振器)

LF:

LowFrequencyCrystalOscillator(低频率的晶体振荡器)

∙工作电压范围:

-EPROM:

2.3V-5.5V

-ROM:

2.3V-5.5V

此说明包含了新产品的一些信息、远翔科技保留修改该产品没有在该文当中说明的特性,由于这些新特性导致的问题远翔科技不承担任何责任、代理商没有任何权力诠释这些特性。

概叙

FM8PS53系列是一款低功耗,高速,高噪声容限,EPROM/ROM基于8位CMOS工艺制造的单片机,采用RISC指令集,共有42条指令,除分支指令为两个周期指令以外其余为单周期指令。

这种易用、易记的指令集大大缩短了开发时间。

FM8P53系列包含了上电复位(Power-onResetPOR),掉电复位(Brown-outResetBOR),上电复位计数器(Power-upResetTimerPWRT),振荡启动计数器(OscillatorStart-upTimerOST),看门狗定时器(WatchdogTimer),EPROM/ROM,SRAM,双向三态I/O口,(可以设置为上拉/下拉、开路),省电睡眠模式,一个带8位预置器的8位定时/计数器,独立中断,睡眠唤醒模式和可靠的代码保护,有两个振荡源可供用户配置选择,包含省电i振荡源和低功耗振荡器.FM8P53系列可访问1K×13的程序存储空间,FM8P53系列能直接或间接访问寄存器以及数据存储区,所有的特殊功能寄存器分布在数据存储区同时包含特定的程序指针。

管脚图

PDIP,SOP

管脚功能描述

管脚名称

I/O

说明

IOA0~IOA3

I/O

IOA0~IOA3双向I/O口

软件可以设置为下拉

IOB0/INT

I/O

双向I/O口同时具有系统唤醒功能

软件设置为上拉/下拉和开路

外部中断输入脚

IOB1

I/O

双向I/O口同时具有系统唤醒功能

软件设置为上拉/下拉和开路

IOB2/T0CKI

I/O

双向I/O口同时具有系统唤醒功能

软件设置为上拉/下拉和开路

外部计数输入脚

IOB3/RSTB

I

IOB3作为输入只能具备系统唤醒功能i

系统复位输入脚.底电平复位.设置为复位输入时上拉

IOB4/OSCO

I/O

双向I/O口同时具有系统唤醒功能(RCOUT可选择IRC/ERIC,ERC模式)

软件设置为上拉/开路

晶体振荡器输出脚(XT,LP模式)

基于指令周期晶体振荡器输出(RCOUT可选择IRC/ERIC,ERC模式)

IOB5/OSCI

I/O

双向I/O口同时具有系统唤醒功能(IRC模式)

软件设置为上拉/开路

晶体振荡器输入脚(XT,LP模式)

外部实时时钟输入脚(ERIC,ERC模式)

IOB6~IOB7

I/O

双向I/O口同时具有系统唤醒功能

软件设置为上拉/开路

Vdd

-

电源

Vss

-

地

Legend:

I=输入,O=输出,I/O=输入/输出

1.0存储器结构

FM8P53存储器包含程序存储器和数据存储器

1.1程序存储器

FM8P53有一个10位PC指针能访问1K×13的存储空间,复位地址为3FFh。

H/W中断向量地址008h.,S/W中断向量地址002h.。

CALL/GOTO能指向在同一个程序页面(一个程序页面为1K)的所有存储空间

程序存储器分布图和堆栈结构

1.2数据存储器

数据存储器包含特殊功能器组和通用寄存器组,所有通用寄存器可以直接寻址或者通过FSR寄存器间接寻址。

特殊功能寄存器用来控制CPU或外围功能模块的工作。

表1.1:

FM8P53寄存器列表

表1.2:

通过OPTION或IOST指令控制的寄存器

地址

说明

B7B6

B5

B4

B3

B2

B1

B0

N/A(w)

OPTION

*INTEDG

T0CS

T0SE

PSA

PS2

PS1

PS0

05h(w)

IOSTA

PortAI/O控制寄存器

06h(w)

IOSTB

PortBI/O控制寄存器

表1.3:

寄存器列表

地址

说明

B7B6B5B4B3B2B1B0

00h(r/w)

INDF

通过FSR访问数据区(不是一个实际的物理地址)

01h(r/w)

TMR0

8位定时/计数器

02h(r/w)

PCL

低8位PC指针

03h(r/w)

STATUS

RST

GP1

GP0TOPDZDCC

04h(r/w)

FSR

*

*

间接地址访问指针(RAM选择寄存器)

05h(r/w)

PORTA

IOA3

IOA2

IOA1

IOA0

06h(r/w)

PORTB

IOB7

IOB6

IOB5

IOB4

IOB3

IOB2

IOB1

IOB0

07h(r/w)

SRAM

通用寄存器

08h(r/w)

PCON

WDTE

EIS

LVDTE

*

*

*

*

*

09h(r/w)

WUCON

WUB7

WUB6

WUB5

WUB4

WUB3

WUB2

WUB1

WUB0

0Ah(r/w)

PCHBUF

-

-

-

-

-

-

2MSBsBufferofPC

0Bh(r/w)

PDCON

/PDB2

/PDB1

/PDB0

/PDA3

/PDA2

/PDA1

/PDA0

0Ch(r/w)

ODCON

ODB7

ODB6

ODB5

ODB4

ODB2

ODB1

ODB0

0Dh(r/w)

PHCON

/PHB7

/PHB6

/PHB5

/PHB4

/PHB2

/PHB1

/PHB0

0Eh(r/w)

INTEN

GIE

*

*

*

*

INTIE

PBIE

T0IE

0Fh(r/w)

INTFLAG

-

-

-

-

-

INTIF

PBIF

T0IF

Legend:

-=unimplemented,readas‘0’,*=unimplemented,readas‘1’,

2.1功能介绍

2.1寄存器操作

2.1.1INDF(间接寻址寄存器)

地址

名称

B7B6B5B4B3B2B1B0

00h(r/w)

INDF

通过FSR访问数据区(不是一个实际的物理地址)

INDF不是一个实际的物理地址,间接寻址时INDF通过RAM选择寄存器(FSR)来访问其所指向的地址。

间接寻址读操作直接读地址00h(FSR=”0”),间接寻址不能对INDF直接进行写操作(尽管有些状态会发生改变),FSR的5-0位可以用来选择64个寄存器(地址:

00h~3Fh)

例2.1:

间接寻址

∙地址38内容为10h

∙地址39内容为0Ah

∙将38写入FSR中

∙通过A读INDF返回10h

∙FSR加1(@FSR=39h)

∙通过A读INDF返回0Ah

2.1.2TMR0(定时/计数器Timelock/Counterregister)

地址

名称

B7B6B5B4B3B2B1B0

01h(r/w)

TMR0

8位定时/计数器

TMR0是一个8位定时/计数器寄存器,Timer0的时钟源可以取值于指令周期或外部实时钟(T0CKIpin),使用外部时钟需要设置OPTION的T0CS(T0CS=5)位为1,

使用TMR0的预置器需要设置OPTION的PSA(PSA=3)位为0,这种模式下TMR0值的改变,预置器被清零

2.1.3PCL(LowBytesofProgramCounter)&Stack

地址

名称

B7B6B5B4B3B2B1B0

02h(r/w)

PCL

8位定时/计数器

FM8P53的PC指针和堆栈的位数为10位,堆栈有5级,低位的PC指针为PCL寄存器,该寄存器时可读写的,高位的PC指针为PCH寄存器,该寄存器包含PC<9:

8>位,该寄存器不能直接读写。

.PCH寄存器的改变是通过PCHBUF寄存器来实现的。

.每一条指令执行的时候他的PC指针包含下一条指令的操作地址。

指令没有改变PC内容时候、在每一个指令周期PC指针自动加1。

对于GOTO指令有PC<9:

0>,PCL映射成PC<7:

0>,PCHBUF不变。

对于CALL指令有PC<9:

0>,下一条指令地址被推进堆栈,PCL映射成PC<7:

0>,PCHBUF不变。

对于RETIA,RETFIE,RETURN指令有PC<9:

0>,PC的内容更改为出栈信息,PCL映射成PC<7:

0>,PCHBUF不变。

对于其他指令,PCLj就是目标信息,PC<7:

0>的内容就是指令地址或。

不管怎样,PC<9:

8>来源于PCHBUF<1:

0>位(PCHBUFPCH).PCHBUF不会改变,从而PCH不会改变。

.

2.2:

不同的指令调用PC指针跳转方式

1、GOTO指令

2、CALL指令

3、RETIA,RETFIE,RETURN指令

注释1.PCHBUF只有在PCL内容是目标地址才有效,当PCL是运算结果时候,PCHBUF不起作用。

2.1.4STATUS(状态字寄存器)

地址

名称

B7B6B5B4B3B2B1B0

03h(r/w)

STATUS

RST

GP1

GP0

TO

PD

Z

DC

C

状态字寄存器包含运算标志,结果标志

指令执行以后可能会影响STATUS寄存器的Z、DC、C标志位,则不能直接对这三个标志位进行写操作,这些标志位的设置由MCU的逻辑自动完成。

同时,TO和PD位也是不能通过指令直接改变写操作。

Therefore,theresultofaninstructionwiththeSTATUSRegisterasdestinationmaybedifferentthanintended.例如:

运行CLRRSTATUS将把STATUS的高三位置零和Z标志位置1同时该寄存器的内容如下

C:

进位标志

ADDAR,ADDIA

=1,有进位

=0,无进位

SUBAR,SUBIA

=1,无借位

=0,有借位

注释:

Asubtractionisexecutedbyaddingthetwo’scomplementofthesecondoperand.Forrotate(RRR,RLR)instructions,thisbitisloadedwitheitherthehighorloworderbitofthesourceregister.

DC:

辅助进位/借位标志.(低四位向高四位进位/借位标志)

ADDAR,ADDIA

=1,底4位有进位

=0,底4位无进位

SUBAR,SUBIA

=1,底4位无借位

=0,底4位有借位

Z:

Zerobit.

=1,算术或逻辑运算结果为“0”时.

=0,算术或逻辑运算结果不为“0”时.

PD:

Powerdownflagbit.

=1,当系统上电时或执行“CLRWDT”指令后

=0,当执行“SLEEP”指令后.

TO:

Timeoverflowflagbit.

=1,当系统上电时或执行“CLRWDT”或SLEEP指令后

=0,看门狗定时器溢出

GP1:

GP0:

通用寄存器读/写位.

RST:

定义系统复位类型位.

=1,唤醒SLEEP或PortB脚位变化唤醒SLEEP

=0,其他类型唤醒SLEEP.

2.1.5FSR(间接寻址指针)

地址

名称

B7B6B5B4B3B2B1B0

04h(r/w)

FSR

*

*

间接寻址指针

PD

Z

DC

C

Bit5:

Bit0:

用来选择访问间接寻址时目标寄存器地址.具体描述见2.1.1。

Bit7:

Bit6:

没有使用.Readas“1”s.

2.1.6PORTA,PORTB(Port寄存器)

地址

名称

B7

B6

B5

B4

B3

B2

B1

B0

05h(r/w)

PORTA

IOA3

IOA2

IOA1

IOA0

06h(r/w)

PORTB

IOB7

IOB6

IOB5

IOB4

IOB3

IOB2

IOB1

IOB0

读端口(PORTA,PORTB寄存器)的状态依赖于该端口是输入/输出模式,写端口是向锁存器写数据

PORTA是一个4位端口数据寄存器,只有低4位被使用(PORTA<3:

0>).Bits7-4通常作为读/写位.

PORTB是一个8位端口数据寄存器.IOB3只能作为输入.

2.1.7PCON(电源控制寄存器)

地址

名称

B7

B6

B5

B4

B3

B2

B1

B0

08h(r/w)

PCON

WDTE

EIS

LVDTE

*

*

*

*

*

Bit4:

Bit0:

Notused.置“1”.

LVDTE:

LVDT(低电压检测)使能位.

=0,关闭LVDT.

=1,使能LVDT.

EIS:

定义管脚B0/INT功能位

=0,IOB0(双向I/O口)isselected.屏蔽了INT功能.

=1,INT(外部中断输入脚),在这种模式下,PORTB的IOB0必须置“1”.IOB0作为I/O口输入功能通过硬件屏蔽了,读取INT管脚信息的与读PORTB.方式相同。

WDTE:

WDT(watch-dogtimer)使能看门狗定时器

=0,关闭WDT.

=1,使能WDT.

2.1.8WUCON(PortB输入改变/唤醒控制寄存器)

地址

名称

B7

B6

B5

B4

B3

B2

B1

B0

09h(r/w)

WUCON

WUB7

WUB6

WUB5

WUB4

WUB3

WUB2

WUB1

WUB0

WUB0:

=0,禁止IIOB0输入改变/唤醒功能

=1,使能IOB0输入改变/唤醒功能.

WUB1:

=0,禁止IIOB1输入改变/唤醒功能

=1,使能IOB1输入改变/唤醒功能.

WUB2:

=0,禁止IIOB2输入改变/唤醒功能

=1,使能IOB2输入改变/唤醒功能.

WUB3:

=0,禁止IIOB3输入改变/唤醒功能

=1,使能IOB3输入改变/唤醒功能.

WUB4:

=0,禁止IIOB4输入改变/唤醒功能

=1,使能IOB4输入改变/唤醒功能.

WUB5:

=0,禁止IIOB5输入改变/唤醒功能

=1,使能IOB5输入改变/唤醒功能.

WUB6:

=0,禁止IIOB6输入改变/唤醒功能

=1,使能IOB6输入改变/唤醒功能.

WUB7:

=0,禁止IIOB7输入改变/唤醒功能

=1,使能IOB7输入改变/唤醒功能.

2.1.9PCHBUF(PC指针高位缓冲区)

Bit1:

Bit0:

见2.1.3

Bit7:

Bit2:

没有使用,置“0”.

2.1.10PDCON(I/O下拉控制寄存器)

地址

名称

B7

B6

B5

B4

B3

B2

B1

B0

0Bh(r/w)

PDCON

/PDB2

/PDB1

/PDB0

/PDA3

/PDA2

/PDA1

/PDA0

/PDA0:

=0,使能IOA0内部下拉

=1,禁止IOA0内部下拉.

/PDA1:

=0,使能IOA1内部下拉

=1,禁止IOA1内部下拉.

/PDA2:

=0,使能IOA2内部下拉

=1,禁止IOA2内部下拉.

/PDA3:

=0,使能IOA3内部下拉

=1,禁止IOA3内部下拉.

/PDB0:

=0,使能IOB0内部下拉

=1,禁止IOB0内部下拉

/PDB1:

=0,使能IOB1内部下拉

=1,禁止IOB1内部下拉

/PDB2:

=0,使能IOB2内部下拉

=1,禁止IOB2内部下拉.

Bit7:

一般的读/写位:

2.1.11ODCON(I/O开路控制寄存器

地址

名称

B7

B6

B5

B4

B3

B2

B1

B0

0Ch(r/w)

ODCON

ODB7

ODB6

ODB5

ODB4

ODB2

ODB1

ODB0

ODB0:

=0,禁止IOB0内部开路

=1,使能IOB0内部开路.

ODB1:

=0,禁止IOB1内部开路

=1,使能IOB1内部开路.

ODB2:

=0,禁止IOB2内部开路

=1,使能IOB2内部开路.

Bit3:

一般的读/写位.

ODB4:

=0,禁止IOB4内部开路

=1,使能IOB4内部开路.

ODB5:

=0,禁止IOB5内部开路

=1,使能IOB5内部开路.

ODB6:

=0,禁止IOB6内部开路

=1,使能IOB6内部开路.

ODB7:

=0,禁止IOB7内部开路

=1,使能IOB7内部开路.

2.1.12PHCON(I/O上拉控制寄存器)

地址

名称

B7

B6

B5

B4

B3

B2

B1

B0

0Dh(r/w)

PHCON

PHB7

PHB6

PHB5

PHB4

PHB2

PHB1

PHB0

/PHB0:

=0,使能IOB0内部上拉.

=1,禁止IOB0内部上拉.

/PHB1:

=0,使能IOB1内部上拉.

=1,禁止IOB1内部上拉.

/PHB2:

=0,使能IOB2内部上拉.

=1,禁止IOB2内部上拉.

Bit3:

一般的读/写位.

/PHB4:

=0,使能IOB4内部上拉.

=1,禁止IOB4内部上拉.

/PHB5:

=0,使能IOB5内部上拉.

=1,禁止IOB5内部上拉.

/PHB6:

=0,使能IOB6内部上拉.

=1,禁止IOB6内部上拉.

/PHB7:

=0,使能IOB7内部上拉.

=1,禁止IOB7内部上拉.

2.1.13INTEN(中断屏蔽寄存器)

地址

名称

B7

B6

B5

B4

B3

B2

B1

B0

0Eh(r/w)

INTEN

GIE

*

*

*

*

INTIE

PBIE

T0IE

T0IE:

Timer0溢出中断屏蔽位.

=0,禁止Timer0溢出中断.

=1,使能Timer0溢出中断

PBIE:

PortB输入改变中断屏蔽位.

=0,禁止PortB输入改变中.

=1,使能PortB输入改变中

INTIE:

外部中断屏蔽位

=0,禁止外部中断.

=1,使能外部中断

Bit6:

BIT3:

没有使用.置“1”.

GIE:

中断允许总控位

=0,禁止所有中断.对于睡眠唤醒模式的中断事件,MCU将执行SLEEP后的指令。

.

=1,使能所有没有屏蔽的中断.对于睡眠唤醒模式的中断事件,MCU将跳转到中断地址(008h)。

注释:

在中断事件发生时,GIEB被硬件清零并禁止一切中断,所以GIE以及与该中断相关的中断屏蔽位需要重开启。

RETFIE为退出中断程序并重新设置GIE=1允许中断。

2.1.14INTFLAG(中断标志寄存器)

地址

名称

B7

B6

B5

B4

B3

B2

B1

B0

0Fh(r/w)

INT

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- FM8PS53 中文版

冰点文库所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰点文库所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《财政学》期末习题.docx

《财政学》期末习题.docx