大学课程《FPGA与SOPC设计教程——DE2-115实践(第二版)》PPT 课件:第6章.pptx

大学课程《FPGA与SOPC设计教程——DE2-115实践(第二版)》PPT 课件:第6章.pptx

- 文档编号:18905770

- 上传时间:2024-02-10

- 格式:PPTX

- 页数:213

- 大小:3.22MB

大学课程《FPGA与SOPC设计教程——DE2-115实践(第二版)》PPT 课件:第6章.pptx

《大学课程《FPGA与SOPC设计教程——DE2-115实践(第二版)》PPT 课件:第6章.pptx》由会员分享,可在线阅读,更多相关《大学课程《FPGA与SOPC设计教程——DE2-115实践(第二版)》PPT 课件:第6章.pptx(213页珍藏版)》请在冰点文库上搜索。

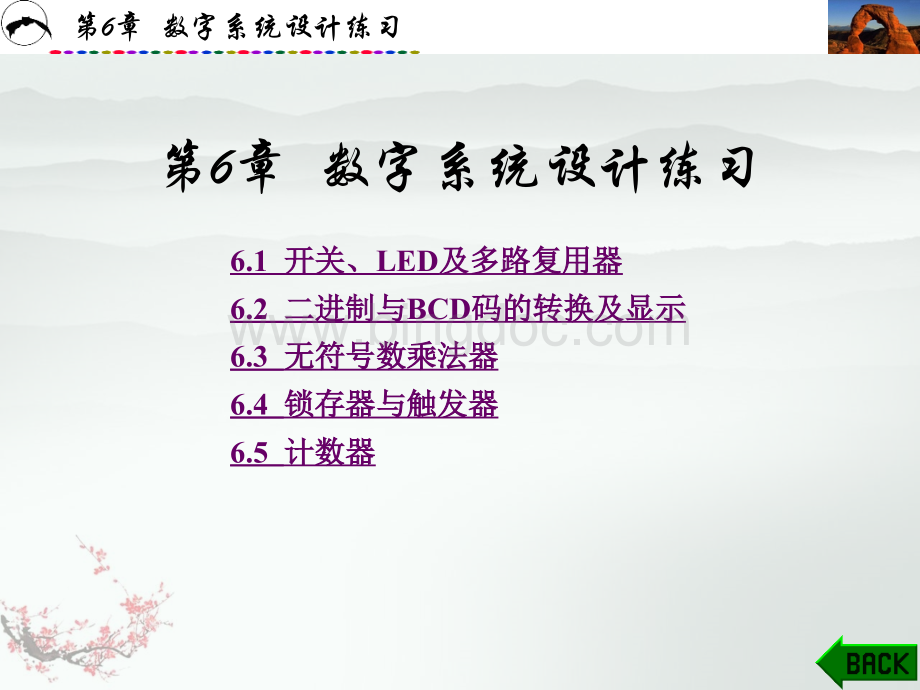

第6章数字系统设计练习第6章数字系统设计练习6.1开关、开关、LED及多路复用器及多路复用器6.2二进制与二进制与BCD码的转换及显示码的转换及显示6.3无符号数乘法器无符号数乘法器6.4锁存器与触发器锁存器与触发器6.5计数器计数器第6章数字系统设计练习第6章数字系统设计练习6.6时钟与定时器时钟与定时器6.7有限状态机有限状态机6.8存储器块存储器块6.9简单的处理器简单的处理器6.10增强型处理器增强型处理器第6章数字系统设计练习6.1开关、开关、LED及多路复用器及多路复用器6.1.1将输入将输入/输出器件连接到输出器件连接到FPGA上上DE2-115平台上提供了18个波段开关,可以作为电路的输入,表示为SW17SW0;还有18个红色LED,表示为LEDR17LEDR0,可以作为输出显示之用。

使用红色LED显示波段开关状态的电路可以用Verilog语言简单地实现,代码如下:

第6章数字系统设计练习由于分别用18个红色LED和18个波段开关,因此在Verilog语言中可以很方便地用向量表示它们,进而可用一个赋值语句完成同样的功能。

DE2-115平台上,LEDR17LEDR0和SW17SW0是与FPGA引脚直接相连的,使用这些引脚之前应该参照本书附录B或者DE2-115用户手册中的引脚分配表,分配连接波段开关和红色LED的FPGA引脚。

例如SW0连接FPGA的PIN_AB28脚,LEDR0连接FPGA的PIN_G19脚。

最简单的方法是在Quartus中导入DE2_115_pin_assignments.csv。

第6章数字系统设计练习为了保证从DE2_115_pin_assignments.csv导入的引脚分配表能够正确使用,在Verilog模块中使用到的引脚名称必须与该文件中的引脚名称完全一致,DE2_115_pin_assignments.csv中用SW0SW17和LEDR0LEDR17分别表示18个波段开关和18个红色LED,因此在编写的Verilog代码中也必须用这种方式来表示。

用向量实现波段开关与红色LED相连的模块代码如代码6.1所示。

第6章数字系统设计练习代码代码6.1将波段开关与红色LED相连的Verilog代码。

modulepart1(SW,LEDR);input17:

0SW;/波段开关output17:

0LEDR;/红色LEDassignLEDR=SW;endmodule第6章数字系统设计练习请按照以下步骤在DE2-115上实现代码6.1并进行测试:

(1)新建一个Quartus工程,用以在DE2-115平台上实现所要求的电路,将FPGA器件选择为EP4CE115F29C7。

(2)建立一个Verilog文件,其内容如代码6.1所示,将该Verilog文件添加到工程中并编译整个工程。

(3)导入DE2_115_pin_assignments.csv中的引脚分配或参照附录B中DE2-115平台的引脚分配表,分配连接波段开关和红色LED的FPGA引脚。

(4)编译该工程,完成后下载到FPGA中。

(5)通过拨动波段开关并观察红色LED的变化来验证所设计的功能是否正确。

第6章数字系统设计练习6.1.2多路复用器多路复用器图6.1(a)是一个2选1多路复用器电路。

如果s=1,则输出m=y;如果s=0,则输出m=x。

图6.1(b)是该电路的真值表。

图6.1(c)是该电路的符号表示。

这个多路复用器可以用以下的Verilog语句来实现:

assignm=(s&x)|(s&y);这部分的练习任务是实现图6.2(a)所示的8位2选1多路复用器,需要用8个赋值语句。

该多路复用器的输入为X和Y,都是8位宽,输出M也为8位宽。

如果s=0,M=X;如果s=1,M=Y。

第6章数字系统设计练习图6.1最简单的多路复用器第6章数字系统设计练习图6.28位2选1多路复用器第6章数字系统设计练习8位2选1多路复用器电路的具体实现步骤如下:

(1)新建一个Quartus工程,用以在DE2-115平台上实现所要求的电路。

(2)新建一个Verilog文件,用SW17作为输入s,以SW7SW0作为输入X,以SW15SW8作为输入Y,将波段开关与红色LED连接以显示其状态,用绿色LED即LEDG7LEDG0作为输出M,将该Verilog文件添加到工程中。

第6章数字系统设计练习(3)导入DE2_115_pin_assignments.csv中的引脚分配或参照附录B中DE2-115平台的引脚分配表,分配连接波段开关、红色LED以及绿色LED的FPGA引脚。

(4)编译工程,完成后下载到FPGA中。

(5)拨动波段开关并观察红色LED与绿色LED的变化,以验证8位2选1多路复用器的功能是否正确。

第6章数字系统设计练习6.1.33位宽位宽5选选1多路复用器多路复用器在完成了基本的2选1多路复用器的基础上,就可以设计复杂的多路复用器,比如3位宽5选1多路复用器,即从5个输入x、y、w、u和v中选取一个输出到m。

这个电路采用了4个2选1的多路复合器来实现,输出选择用一个3位的输入s2s1s0实现。

5选1多路复用器的结构如图6.3(a)所示,真值表如图6.3(b)所示,电路符号表示如图6.3(c)所示。

第6章数字系统设计练习图6.35选1多路复用器第6章数字系统设计练习图6.4实现了一个3位5选1多路复用器,这个电路中包含了3个图6.3(a)所示的电路。

图6.43位5选1多路复用器电路第6章数字系统设计练习请按照以下步骤实现3位5选1多路复用器:

(1)新建一个Quartus工程,用以在DE2-115平台上实现所要求的电路。

(2)建立一个Verilog文件,用SW17SW15作为选择端输入s2s1s0,用剩下的15个波段开关SW14SW0作为输入U、V、W、X、Y,将波段开关与红色LED连接以显示波段开关的状态,用绿色LED即LEDG2LEDG0作为输出M,将该Verilog文件添加到工程中。

第6章数字系统设计练习(3)导入DE2_115_pin_assignments.csv中的引脚分配或参照附录B中DE2-115平台的引脚分配表,分配连接波段开关、红色LED以及绿色LED的FPGA引脚。

(4)编译工程,完成后下载到FPGA中。

(5)拨动波段开关并观察红色LED与绿色LED的变化,以验证3位5选1多路复用器的功能是否正确,确定从U到Y的所有输入都能够被选择输出到M。

第6章数字系统设计练习6.1.4用七段数码管显示简单字符用七段数码管显示简单字符图6.5所示是一个简单的七段解码器模块,c2c1c0是解码器的3个输入,用c2c1c0的不同取值来选择在七段数码管上输出不同的字符。

七段数码管上的不同段位用数字06表示。

注意七段数码管是共阳极的。

表6.1列出了c2c1c0取不同值时数码管上输出的字符。

本例中只输出4个字符,当c2c1c0取值为100111时,输出空格。

第6章数字系统设计练习图6.5七段解码器第6章数字系统设计练习表6.1七段数码管显示字符编码c2c1c0输出字符000011110011001101010101HELO第6章数字系统设计练习请按照以下步骤实现七段解码器电路:

(1)新建一个Quartus工程,用以在DE2-115平台上实现所要求的电路。

(2)建立一个Verilog文件,实现七段解码器电路,用SW2SW0作为输入c2c0,DE2-115平台上的数码管分别为HEX0HEX7,输出接HEX0,在Verilog中用以下语句定义端口:

output0:

6HEX0;第6章数字系统设计练习(3)导入DE2_115_pin_assignments.csv中的引脚分配或参照附录B中DE2-115平台的引脚分配表分配引脚。

(4)编译工程,完成后下载到FPGA中。

(5)拨动波段开关并观察七段数码管HEX0的显示,以验证设计的功能是否正确。

第6章数字系统设计练习6.1.5循环显示循环显示5个字符个字符图6.6中的电路采用了一个3位5选1多路复用电路,可分别从输入的5个字符中选择1个字符并通过七段解码器电路在数码管上显示H、E、L、O和空格中的任一字符。

将SW14SW0分为5组,分别代表H、E、L、O和空格等5个字符,用SW17SW15来选择要显示的字符。

第6章数字系统设计练习图6.6循环显示5个字符的电路第6章数字系统设计练习代码6.2是实现这个电路的建议代码架构,其中部分代码省略,读者可以根据前文的练习自行补全。

在这个电路中我们将6.1.3小节和6.1.4小节中的电路作为子电路。

对代码6.2中的代码进行扩展后,可以用5个数码管显示,当改变SW17SW15的状态时,最终显示的内容与SW17SW15的对应关系如表6.2所示,即可以循环显示单词“HELLO”。

第6章数字系统设计练习第6章数字系统设计练习代码代码6.2图6.6所示电路的Verilog代码。

第6章数字系统设计练习请按照以下步骤实现“HELLO”的循环显示电路:

(1)新建一个Quartus工程,用以在DE2-115平台上实现所要求的电路。

(2)建立一个Verilog文件,用SW17SW15作为5个3位5选1多路复用器的选择输入,按照表6.2的对应关系,将SW14SW0连接到每个多路复用器实例的输入端,将5个多路复用器的输出接到5个七段数码管HEX4HEX0,将Verilog文件添加到工程中来。

第6章数字系统设计练习(3)导入DE2_115_pin_assignments.csv中的引脚分配或参照附录B中DE2-115平台的引脚分配表分配引脚。

(4)编译工程,完成后下载到FPGA中。

(5)按照表6.2设置好SW14SW0的位置,然后改变波段开关SW17SW15的位置,观察显示是否正确。

第6章数字系统设计练习6.1.6循环显示循环显示8个字符个字符在6.1.5小节的基础上,把5个字符扩展到8个字符,如果显示内容少于8个,比如显示“HELLO”,则数码管显示输出与SW17SW15的对应关系如表6.3所示。

第6章数字系统设计练习第6章数字系统设计练习请按照以下步骤实现“HELLO”的循环显示电路:

(1)新建一个Quartus工程,用以在DE2-115平台上实现所要求的电路。

(2)建立一个Verilog文件,这里会用到8个5选1多路复用器的电路,用SW17SW15作为8个3位5选1多路复用器的选择输入,按照表6.3的对应关系,将SW14SW0连接到每个多路复用器电路的输入端(有些多路复用器的输入会是空格),将8个多路复用器的输出接到8个七段数码管HEX7HEX0上,将Verilog文件添加到工程中来。

第6章数字系统设计练习(3)导入DE2_115_pin_assignments.csv中的引脚分配或参照附录B中DE2-115平台的引脚分配表分配引脚。

(4)编译工程,完成后下载到FPGA中。

(5)按照表6.3设置好SW14SW0的位置,然后改变波段开关SW17SW15的位置,观察循环显示是否正确。

第6章数字系统设计练习6.2二进制与二进制与BCD码的转换及显示码的转换及显示1二进制数字的显示二进制数字的显示在HEX3HEX0上显示SW15SW0所对应的二进制数字,SW15SW12、SW11SW8、SW7SW4和SW3SW0分别对应HEX3、HEX2、HEX1和HEX0。

在数码管上只显示数字09,当波段开关表示的二进制数字在10101111之间时,没有显示输出。

第6章数字系统设计练习显示二进制数字的具体步骤如下:

(1)新建一个Quartus工程,用以在DE2-115平台上实现所要求的电路。

(2)建立一个Verilog文件,实现要求的任务。

本练习的目的是手工推导出数码管显示的逻辑函数,因此要求只能用assign语句和布尔表达式实现所有的功能。

(3)导入DE2_115_pin_assignments.csv中的引脚分配或参照附录B中DE2-115平台的引脚分配表分配引脚。

(4)编译工程,完成后下载到FPGA中。

(5)改变SW15SW0的位置,观察显示是否正确。

第6章数字系统设计练习2二进制值到十进制值的转换二进制值到十进制值的转换若将4位二进制输入V=v3v2v1v0转换成2位十进制的等价表示D=d1d0,在HEX1和HEX0上分别显示d1和d0,则输入的二进制值与输出的十进制值之间的对应关系如表6.4所示。

图6.7是实现这个任务的部分电路,比较器判断V是否大于9,比较器的输出z可以控制数码管的显示。

第6章数字系统设计练习第6章数字系统设计练习图6.7显示二进制数值的电路第6章数字系统设计练习完成下面的操作步骤:

(1)新建一个Quartus工程,用以在DE2-115平台上实现所要求的电路。

(2)建立一个Verilog文件,包括电路中的比较器、多路复用器和电路A,但不包括电路B和七段解码器。

这个模块的输入为4位二进制数V,输出是z和4位的M。

编写这个模块时只能用assign语句和布尔表达式实现所要求的功能,而不能出现if-else和case等语句。

(3)编译工程并仿真,验证比较器、多路复用器和电路A的正确性。

第6章数字系统设计练习(4)修改Verilog代码,加入电路B和七段解码器,用SW3SW0作为二进制输入,而用HEX1和HEX0作为十进制输出的显示。

(5)导入DE2_115_pin_assignments.csv中的引脚分配或参照附录B中DE2-115平台的引脚分配表分配引脚。

(6)重新编译工程,完成后下载到FPGA中。

(7)改变SW3SW0的位置,遍历输入V的各种组合,观察输出显示是否正确。

第6章数字系统设计练习3并行加法器并行加法器一位二进制全加器电路如图6.8(a)所示,输入为a、b和ci,输出为s和co;图6.8(b)是该电路的符号表示;图6.8(c)是全加器的真值表。

全加器实现了二进制加法,其输出为一个2位二进制和,即cos=a+b+ci。

用4个全加器电路模块可以实现4位二进制数的加法,如图6.8(d)所示,这种加法电路一般称为并行加法器。

第6章数字系统设计练习图6.8全加器及并行加法器第6章数字系统设计练习实现并行加法器电路的步骤如下:

(1)为并行加法器建立一个新的Quartus工程文件。

(2)用Verilog编写一个全加器电路模块,然后用4个全加器电路来实现并行加法器电路。

(3)分别用SW7SW4和SW3SW0代表输入a和b,使用SW8代表加法器的进位输入ci,将SW8SW0直接连接到LEDR8LEDR0,而将加法器的输出co和s连接到LEDG4LEDG0,将代码添加到工程中。

第6章数字系统设计练习(4)导入DE2_115_pin_assignments.csv中的引脚分配或参照附录B中DE2-115平台的引脚分配表分配引脚。

(5)编译工程,完成后下载到FPGA中。

(6)改变输入a、b和ci的值,观察计算输出结果是否正确。

第6章数字系统设计练习41位位BCD加法器加法器在前面的练习中,实现了二进制数到十进制数的转换,而在有些场合,我们需要用二进制数表示十进制数,就是将十进制数的每一位用4位二进制数来表示,比如将十进制数59表示为二进制数01011001。

这种用4位二进制数表示十进制数的编码,称为BCD码。

本练习的任务是实现BCD码的加法,输入为两个BCD码A和B以及1位的进位输入,输出是和的BCD码S1S0。

这个电路能够处理的和的最大值为S1S0=9+9+1=19。

第6章数字系统设计练习请按照以下步骤完成练习:

(1)为BCD加法器新建一个Quartus工程。

(2)建立一个Verilog文件,实现要求的任务。

先用前面介绍的并行加法器实现4位二进制加法,输入为A+B的4位和S1S0及进位位输出co。

然后再设计一个二进制到十进制的转换电路,注意最大输出为19。

编写这个模块时只能用assign语句和布尔表达式实现所要求的功能,而不能出现if-else和case等语句。

第6章数字系统设计练习(3)将编写好的Verilog文件添加到工程中,导入DE2_115_pin_assignments.csv中的引脚分配或参照附录B中DE2-115平台的引脚分配表分配引脚。

(4)编译工程,完成后下载到FPGA中。

(5)输入不同的A、B和ci,验证输出S是否正确。

第6章数字系统设计练习52位位BCD加法器加法器若设计一个2位BCD加法器,计算两个2位BCD码A1A0和B1B0的和,输出为3位BCD码S2S1S0,则可以用两个1位BCD加法器来实现。

请按照以下步骤完成练习:

(1)用SW15SW8和SW7SW0分别表示两个BCD码输入A1A0和B1B0,A1A0的值显示在数码管HEX7和HEX6上,B1B0的值显示在数码管HEX5和HEX4上,S2S1S0显示在数码管HEX2HEX0上。

第6章数字系统设计练习

(2)导入DE2_115_pin_assignments.csv中的引脚分配或参照附录B中DE2-115平台的引脚分配表分配引脚。

(3)编译工程,完成后下载到FPGA中。

(4)输入不同的A1A0和B1B0的值,验证输出S2S1S0是否正确。

第6章数字系统设计练习6.2位位BCD加法器的另一种实现加法器的另一种实现在前面的练习中,通过调用两个1位BCD加法器实现了一个2位BCD加法器。

在本练习中,我们按代码6.3描述的算法重新设计一个2位BCD加法器。

第6章数字系统设计练习代码代码6.3实现2位BCD加法器的伪代码。

第6章数字系统设计练习这个伪代码用电路实现起来很容易,第1、9、10和18行可用加法器实现,第28行及第1117行是多路复用器,可以用比较器判断T09和T19。

用Verilog代码实现这段伪代码时,注意第9行和第18行的减法可以用加法实现。

该伪代码中使用了if-else结构以及“”及“+”等运算,比实际的电路要抽象一些,其目的是让Verilog编译器去决定具体电路的实现。

第6章数字系统设计练习请按照以下步骤完成练习:

(1)建立新的Quartus工程,所有的输入、输出以及显示都与2位BCD加法器的第一种实现方法相同,参照代码6.3所示的伪代码编写一个Verilog文件,并添加到工程中去。

(2)编译该工程,用Quartus的RTLViewer工具查看编译后生成的电路,并与第一种方法中的电路进行比较。

(3)把编译后电路下载到FPGA中。

(4)对电路进行功能验证。

第6章数字系统设计练习7.6位二进制数转换为位二进制数转换为2位十进制数的电路位十进制数的电路用Verilog语言实现一个电路,将6位二进制数转换成2位BCD编码的十进制数,用SW5SW0作为6位二进制数输入,用HEX1和HEX0显示2位十进制数,完成后在DE2-115上验证该电路。

第6章数字系统设计练习6.3无符号数乘法器无符号数乘法器14位二进制数乘法位二进制数乘法图6.9(a)为两位十进制数乘法的实现,即P=AB,其中A=12,B=11,P=132;图6.9(b)是用4位二进制乘法实现的A和B的乘积,对于二进制乘法,B的每一位要么是0,要么是1,因此算式中的加法要么是移位的A,要么是0000;图6.9(c)是用逻辑与实现二进制乘法的过程。

第6章数字系统设计练习图6.9二进制数相乘第6章数字系统设计练习图6.10是4位二进制乘法器的实现电路。

该电路中,用逻辑与实现每一行的乘法,用全加器实现每一列的加法,从而得到所需要的和。

根据这种乘法器的结构,我们把它称作矩阵乘法器。

请按照以下步骤完成本练习:

(1)新建一个Quartus工程,用以在DE2-115平台上实现所要求的电路。

(2)建立一个Verilog文件,实现要求的任务。

编译工程,仿真并验证代码的正确性。

第6章数字系统设计练习(3)用SW11SW8表示输入A,用SW3SW0表示输入B,将A和B的十六进制值分别用HEX6和HEX4显示,将P=AB的结果用HEX1和HEX0显示。

(4)重新编译工程,完成后下载到FPGA中。

(5)改变相关波段开关的位置,观察输出显示是否正确。

第6章数字系统设计练习图6.104位二进制乘法器的实现电路第6章数字系统设计练习2.8位二进制数乘法位二进制数乘法参照4位二进制数乘法器电路,将乘数A和B扩展到8位宽,用SW15SW8和SW7SW0分别表示乘数A和B,A和B的十六进制值分别在HEX7HEX6和HEX5HEX4上显示,16位乘积输出P=AB在HEX3HEX0上显示。

第6章数字系统设计练习3用用LPM实现实现8位二进制数乘法位二进制数乘法用Quartus软件中提供的参数化功能模块lpm_mult实现8位二进制无符号数的乘法。

完成后,与用Verilog实现的8位二进制数乘法器电路比较,看这两种实现方法所占用的逻辑单元的数量有什么不同。

第6章数字系统设计练习6.4锁存器与触发器锁存器与触发器6.4.1RS锁存器锁存器Intel公司的FPGA内有可供用户使用的触发器电路。

在本节的练习中我们首先探讨如何不使用专用触发器而在FPGA内部构造存储单元。

第6章数字系统设计练习图6.11是一个门控RS锁存电路。

这个锁存电路可以使用两种方法来实现:

第一种方法是使用逻辑门电路来实现,如代码6.4所示;第二种方法则使用逻辑表达式来实现,如代码6.5所示。

如果在一个含有4输入查找表的FPGA中实现这个电路,那么只需一个查找表即可,如图6.12(a)所示。

第6章数字系统设计练习图6.11门控RS锁存器第6章数字系统设计练习图6.12在FPGA上实现门控RS锁存器第6章数字系统设计练习代码代码6.4用逻辑门电路实现的RS锁存器。

第6章数字系统设计练习代码代码6.5用逻辑表达式实现的RS锁存器。

第6章数字系统设计练习在图6.12(a)中,尽管用一个4输入查找表就可以实现门控RS锁存器,但使用这种方法无法观察锁存器的内部信号,比如R_g和S_g信号。

为了能够观察到这两个内部信号,需要使用编译指令,在上面的Verilog代码中出现的/*synthesiskeep*/就是编译指令,要求Quartus在编译R_g、S_g、Qa和Qb信号时各自采用独立的逻辑单元。

编译后生成的电路如图6.12(b)所示。

第6章数字系统设计练习请按照以下步骤完成练习:

(1)为RS锁存器新建一个Quartus工程,用以在DE2-115平台上实现所要求的电路。

(2)建立一个Verilog文件,采用代码6.4或者代码6.5(两种代码生成的电路是一样的),将这个Verilog文件添加到工程中去。

(3)编译这个工程,用RTLViewer工具查看代码生成的门级电路,然后用TechnologyMapViewer工具查看锁存器是否是按图6.12(b)所示方式实现的。

(4)编写Testbench文件,用Modelsim仿真工具对电路进行仿真验证。

第6章数字系统设计练习6.4.2D锁存器锁存器图6.13所示是一个D锁存器电路。

图6.13D锁存器电路第6章数字系统设计练习请按照以下步骤完成练习:

(1)为D锁存器新建一个Quartus工程。

(2)建立一个Verilog文件,采用类似于代码6.4和代码6.5的代码,实现图6.13中的D锁存器。

在Verilog代码中采用编译指令/*synthesiskeep*/以保证编译时编译器采用独立的逻辑单元实现R、R_g、S_g、Qa和Qb信号。

(3)用RTLViewer工具查看代码生成的门级电路,然后用TechnologyMapViewer工具查看锁存器在FPGA中的实现。

第6章数字系统设计练习(4)再新建一个Verilog文件,用以在DE2-115平台上实现D锁存器。

(5)建立一个顶层文件,在顶层文件中使用一个D锁存器来定义相应的输入/输出引脚,用SW0作为输入D,用SW1作为Clk,并将Q连接到LEDR0。

(6)编译工程,并将电路下载到DE2-115开发板上。

(7)对电路进行功能测试。

第6章数字系统设计练习6.4.3D触发器触发器图6.14是一个主从式D触发器电路。

图6.14主

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- FPGA与SOPC设计教程DE2-115实践第二版 大学课程FPGA与SOPC设计教程DE2-115实践第二版PPT 课件:第6章 大学 课程 FPGA SOPC 设计 教程 DE2

冰点文库所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰点文库所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

链接地址:https://www.bingdoc.com/p-18905770.html

XX大学20XX-20YY学年本科教学质量报告(专业完整模板).docx

XX大学20XX-20YY学年本科教学质量报告(专业完整模板).docx