VerilogHDL电梯程序文件文档格式.docx

VerilogHDL电梯程序文件文档格式.docx

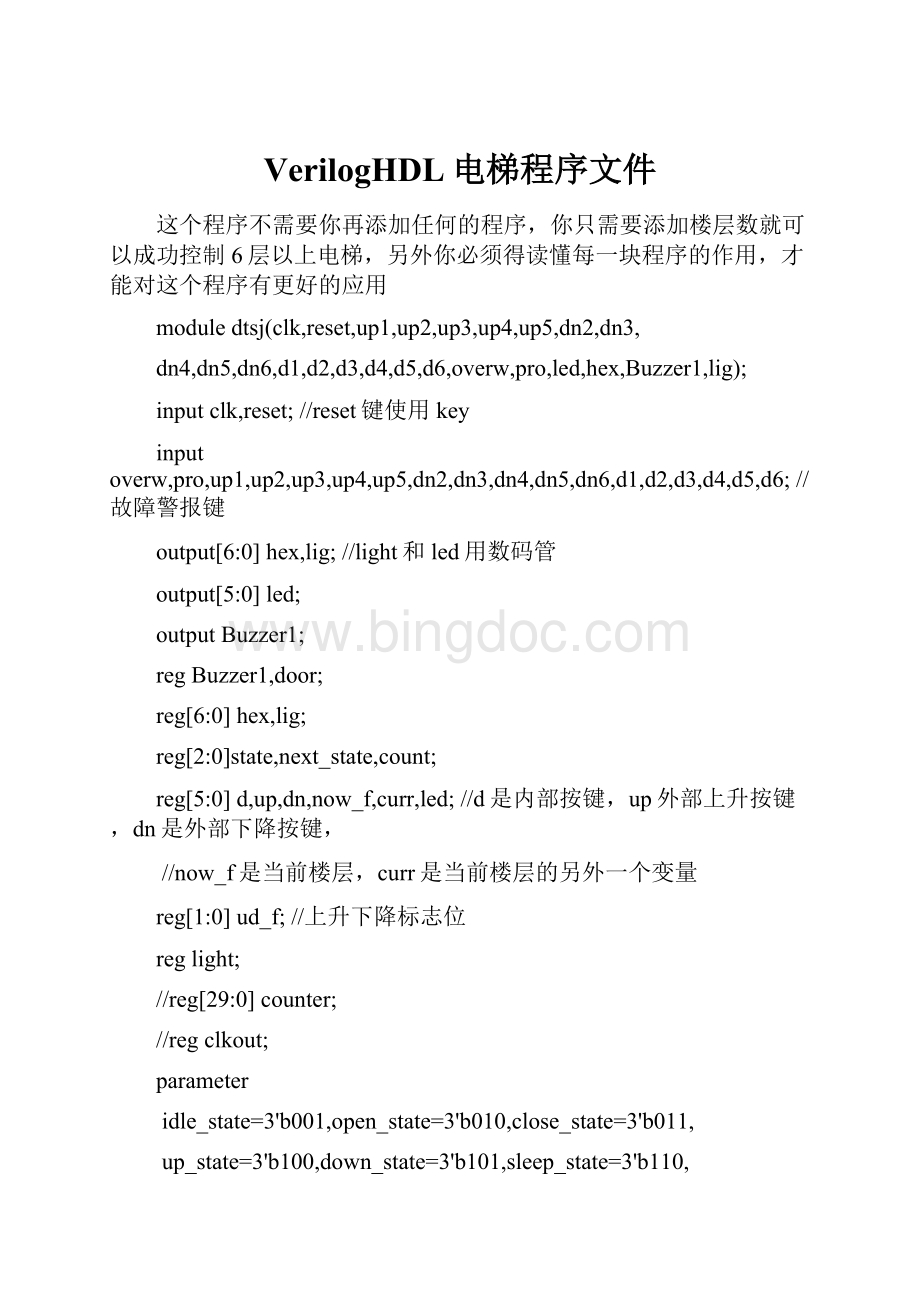

- 文档编号:4059670

- 上传时间:2023-05-02

- 格式:DOCX

- 页数:14

- 大小:16.10KB

VerilogHDL电梯程序文件文档格式.docx

《VerilogHDL电梯程序文件文档格式.docx》由会员分享,可在线阅读,更多相关《VerilogHDL电梯程序文件文档格式.docx(14页珍藏版)》请在冰点文库上搜索。

0]ud_f;

//上升下降标志位

reglight;

//reg[29:

0]counter;

//regclkout;

parameter

idle_state=3'

b001,open_state=3'

b010,close_state=3'

b011,

up_state=3'

b100,down_state=3'

b101,sleep_state=3'

b110,

alarm_state=3'

b111,f1=6'

b000001,f2=6'

b000010,f3=6'

b000100,f4=6'

b001000

f5=6'

b010000,f6=6'

b100000,up_f=2'

b01,dn_f=2'

b10,idle=2'

b00;

//jiuzhongzhuangtaiheshangshengzhuangtai'

shangshengzhuangtaihexiajiazhuangtai

initial

begin

state<

=idle_state;

end

always@(posedgeclkorposedgereset)

if(reset)

else

=next_state;

always@(stateorupordnordornow_forcountorud_f)

case(state)

open_state:

begin

if(count<

5)

next_state=open_state;

else

next_state=close_state;

end

sleep_state:

if((up||dn||d||ud_f)==0)

next_state=idle_state;

idle_state:

//初始状态

next_state=sleep_state;

if(!

overw||pro==1)

next_state=alarm_state;

elseif(d>

0)

if((d&

now_f)>

now_f)

next_state=up_state;

next_state=down_state;

elseif((up&

now_f)||(dn&

now_f))

elseif((up>

now_f)||(dn>

elseif(up||dn)

up_state:

elseif((d&

now_f)||(up&

elseif((d>

now_f)||(up>

elseif((d<

now_f)||(up<

now_f))//elseif(d||up)waitspeak

elseif(dn>

if(dn>

elseif((dn&

now_f)||(now_f<

f6))

now_f)&

&

(now_f==f6))

down_state:

elseif(!

elseif(((d<

(d!

=6'

b000001))||((dn<

(dn!

b000001)))

elseif(up>

if(up<

now_f)

(now_f>

f1))

(now_f==f1))

close_state:

elseif(ud_f==up_f)

elseif(d||up)

elseif(ud_f==dn_f)

b000000))||((dn<

b000000)))

elseif(d||dn)

0)

if(up<

if(d>

(dn&

(dn>

alarm_state:

//Buzzer1<

=1'

b1;

b0;

next_state<

=up_state;

default:

endcase

always@(up1orup2orup3orup4orup5)

up={1'

b0,up5,up4,up3,up2,up1};

always@(dn2ordn3ordn4ordn5ordn6)

dn={dn6,dn5,dn4,dn3,dn2,1'

b0};

always@(d1ord2ord3ord4ord5ord6)

d={d6,d5,d4,d3,d2,d1};

always@(posedgeclkorposedgereset)

if(reset)

count<

=0;

elseif((next_state==open_state)&

(count<

5))

=count+1;

always@(posedgeclkorposedgereset)

//always@(resetornext_state)

if(reset)

now_f<

=f1;

ud_f<

=idle;

led<

b000001;

light<

=now_f;

curr=now_f;

case(next_state)

=led;

curr<

Buzzer1<

=now_f<

<

1;

=up_f;

=led+1;

=now_f>

>

=dn_f;

=ud_f;

door<

=door;

b000000;

always@(curr)

begin

case(curr)

6'

b000001:

hex=7'

b1111001;

//数码管共阴共阳

b000010:

b1000100;

b000100:

b0110000;

b001000:

b0011001;

b010000:

b1101101;

b100000:

b1111101;

b0000000;

endcase

end

always@(light)

case(light)

1'

b0:

lig=7'

b1000000;

//1'

b1:

light=7'

//分频程序

/*always@(posedgeclk)

if(counter[29:

0]==24999999)

begin//每计到4个(0~3)上升沿,输出信号翻转一次

counter<

=0;

clkout<

=~clkout;

counter[29:

0]<

=counter[29:

0]+1'

end*/

endmodule

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- VerilogHDL 电梯 程序 文件

冰点文库所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰点文库所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

建筑工程编制依据及概况.docx

建筑工程编制依据及概况.docx