EDA数字跑表.docx

EDA数字跑表.docx

- 文档编号:4187937

- 上传时间:2023-05-06

- 格式:DOCX

- 页数:14

- 大小:125.17KB

EDA数字跑表.docx

《EDA数字跑表.docx》由会员分享,可在线阅读,更多相关《EDA数字跑表.docx(14页珍藏版)》请在冰点文库上搜索。

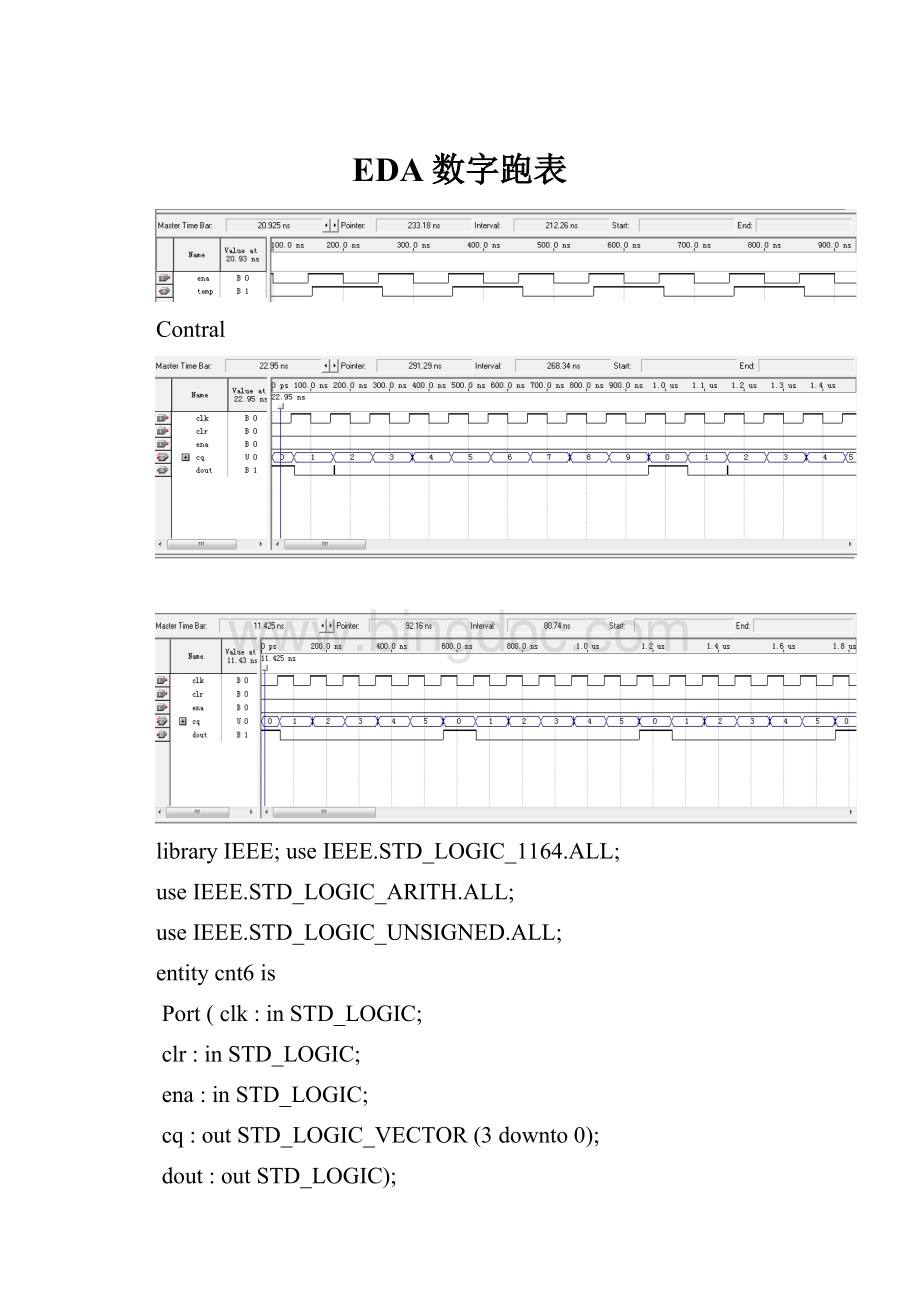

EDA数字跑表

Contral

libraryIEEE;useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_ARITH.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

entitycnt6is

Port(clk:

inSTD_LOGIC;

clr:

inSTD_LOGIC;

ena:

inSTD_LOGIC;

cq:

outSTD_LOGIC_VECTOR(3downto0);

dout:

outSTD_LOGIC);

endcnt6;

architectureBehavioralofcnt6is

signalcqi:

std_logic_vector(3downto0):

="0000";

begin

cq<=cqi;

process(clk,clr,ena)

begin

ifclr='1'then

cqi<="0000";

elsifrising_edge(clk)then

ifena='0'then

ifcqi="0101"then

cqi<="0000";

else

cqi<=cqi+1;

endif;

endif;

endif;

endprocess;

process(cqi)

begin

ifcqi="0000"then

dout<='1';

else

dout<='0';

endif;

endprocess;

endBehavioral;

--************************************

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_ARITH.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

entitycnt10is

Port(clk:

inSTD_LOGIC;

clr:

inSTD_LOGIC;

ena:

inSTD_LOGIC;

cq:

outSTD_LOGIC_VECTOR(3downto0);

dout:

outSTD_LOGIC);

endcnt10;

architectureBehavioralofcnt10is

signalcqi:

std_logic_vector(3downto0):

="0000";

begin

cq<=cqi;

process(clk,clr,ena)

begin

ifclr='1'then

cqi<="0000";

elsifrising_edge(clk)then

ifena='0'then

ifcqi="1001"then

cqi<="0000";

else

cqi<=cqi+1;

endif;

endif;

endif;

endprocess;

process(clk,clr,ena)

begin

ifcqi="0000"then

dout<='1';

else

dout<='0';

endif;

endprocess;

endBehavioral;

--************************************

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_ARITH.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

entitycontrolis

Port(ena:

inSTD_LOGIC;

temp:

outSTD_LOGIC);

endcontrol;

architectureBehavioralofcontrolis

begin

process(ena)

begin

temp<=ena;

endprocess;

endBehavioral;

--***********************************

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_ARITH.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

entitydisplayis

Port(clkin:

inSTD_LOGIC;

s6:

inSTD_LOGIC_VECTOR(3downto0);

s5:

inSTD_LOGIC_VECTOR(3downto0);

s4:

inSTD_LOGIC_VECTOR(3downto0);

s3:

inSTD_LOGIC_VECTOR(3downto0);

s2:

inSTD_LOGIC_VECTOR(3downto0);

s1:

inSTD_LOGIC_VECTOR(3downto0);

--g:

inSTD_LOGIC;

G:

OUTSTD_LOGIC;

display:

outSTD_LOGIC_VECTOR(7downto0);

sel:

outSTD_LOGIC_VECTOR(2downto0));

enddisplay;

architectureBehavioralofdisplayis

signalcnt:

integerrange0to5:

=0;

begin

process(clkin)--g)

variablenum:

std_logic_vector(3downto0);

begin

ifrising_edge(clkin)--and--g='0'

then

ifcnt=5then

cnt<=0;

else

cnt<=cnt+1;

endif;

casecntis

when0=>sel<="000";num:

=s1;

when1=>sel<="001";num:

=s2;

when2=>sel<="010";num:

=s3;

when3=>sel<="011";num:

=s4;

when4=>sel<="100";num:

=s5;

when5=>sel<="101";num:

=s6;

endcase;

casenumis

when"0000"=>display<="00000011";

when"0001"=>display<="10011111";

when"0010"=>display<="00100101";

when"0011"=>display<="00001101";

when"0100"=>display<="10011001";

when"0101"=>display<="01001001";

when"0110"=>display<="01000001";

when"0111"=>display<="00011111";

when"1000"=>display<="00000001";

when"1001"=>display<="00001001";

whenothers=>display<="11111101";

endcase;

endif;

endprocess;

endBehavioral;

--*****************************************

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_ARITH.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

entityfenpis

Port(clkin:

inSTD_LOGIC;

clkout100:

outSTD_LOGIC;

clkout1k:

outSTD_LOGIC);

endfenp;

architectureBehavioraloffenpis

signalcnt100:

integerrange1to240;

signalcnt1k:

integerrange1to24;

signalclk100:

std_logic:

='0';

signalclk1k:

std_logic:

='0';

begin

process(clkin)

begin

ifrising_edge(clkin)then

ifcnt100=240then

cnt100<=1;

clk100<=notclk100;

else

cnt100<=cnt100+1;

endif;

endif;

ifrising_edge(clkin)then

ifcnt1k=24thencnt1k<=1;

clk1k<=notclk1k;

else

cnt1k<=cnt1k+1;

endif;

endif;

endprocess;

clkout100<=clk100;

clkout1k<=clk1k;

endBehavioral;

--*****************************************

libraryieee;

useieee.std_logic_1164.ALL;

useieee.numeric_std.ALL;

--libraryUNISIM;

--useUNISIM.Vcomponents.ALL;

entityZLis

port(CLKIN:

instd_logic;

clr:

instd_logic;

ena:

instd_logic;

DIS:

outstd_logic_vector(7downto0);

G:

outstd_logic;

--G:

instd_logic;

sel:

outstd_logic_vector(2downto0));

endZL;

architectureBEHAVIORALofZLis

signalXLXN_1:

std_logic;

signalXLXN_2:

std_logic;

signalXLXN_3:

std_logic;

signalXLXN_4:

std_logic;

signalXLXN_5:

std_logic;

signalXLXN_6:

std_logic;

signalXLXN_7:

std_logic;

signalXLXN_9:

std_logic;

signalXLXN_13:

std_logic_vector(3downto0);

signalXLXN_14:

std_logic_vector(3downto0);

signalXLXN_15:

std_logic_vector(3downto0);

signalXLXN_16:

std_logic_vector(3downto0);

signalXLXN_17:

std_logic_vector(3downto0);

signalXLXN_18:

std_logic_vector(3downto0);

signalXLXI_6_clr_openSignal:

std_logic;

signalXLXI_6_ena_openSignal:

std_logic;

componentcnt10

port(clk:

instd_logic;

clr:

instd_logic;

ena:

instd_logic;

dout:

outstd_logic;

cq:

outstd_logic_vector(3downto0));

endcomponent;

componentcnt6

port(clk:

instd_logic;

clr:

instd_logic;

ena:

instd_logic;

dout:

outstd_logic;

cq:

outstd_logic_vector(3downto0));

endcomponent;

componentdisplayport(clkin:

instd_logic;

s6:

instd_logic_vector(3downto0);

s5:

instd_logic_vector(3downto0);

s4:

instd_logic_vector(3downto0);

s3:

instd_logic_vector(3downto0);

s2:

instd_logic_vector(3downto0);

s1:

instd_logic_vector(3downto0);

display:

outstd_logic_vector(7downto0);

sel:

outstd_logic_vector(2downto0);

G:

outstd_logic);

--G:

instd_logic);

endcomponent;

componentfenp

port(clkin:

instd_logic;

clkout100:

outstd_logic;

clkout1k:

outstd_logic);

endcomponent;

componentcontrol

port(ena:

instd_logic;

temp:

outstd_logic);

endcomponent;

begin

XLXI_1:

cnt10

portmap(clk=>XLXN_1,

clr=>clr,

ena=>XLXN_9,

cq(3downto0)=>XLXN_13(3downto0),

dout=>XLXN_3);

XLXI_2:

cnt10

portmap(clk=>XLXN_3,

clr=>clr,

ena=>XLXN_9,

cq(3downto0)=>XLXN_14(3downto0),

dout=>XLXN_4);

XLXI_3:

cnt10

portmap(clk=>XLXN_4,

clr=>clr,

ena=>XLXN_9,

cq(3downto0)=>XLXN_15(3downto0),

dout=>XLXN_5);

XLXI_4:

cnt6

portmap(clk=>XLXN_5,

clr=>clr,

ena=>XLXN_9,

cq(3downto0)=>XLXN_16(3downto0),

dout=>XLXN_6);

XLXI_5:

cnt10

portmap(clk=>XLXN_6,

clr=>clr,

ena=>XLXN_9,

cq(3downto0)=>XLXN_17(3downto0),

dout=>XLXN_7);

XLXI_6:

cnt6

portmap(clk=>XLXN_7,

clr=>clr,---XLXI_6_clr_openSignal,

ena=>XLXN_9,--XLXI_6_ena_openSignal,

cq(3downto0)=>XLXN_18(3downto0),

dout=>open);

XLXI_7:

display

portmap(clkin=>XLXN_2,

s1(3downto0)=>XLXN_13(3downto0),

s2(3downto0)=>XLXN_14(3downto0),

s3(3downto0)=>XLXN_15(3downto0),

s4(3downto0)=>XLXN_16(3downto0),

s5(3downto0)=>XLXN_17(3downto0),

s6(3downto0)=>XLXN_18(3downto0),

display(7downto0)=>DIS(7downto0),

G=>G,

sel(2downto0)=>sel(2downto0));

XLXI_8:

fenp

portmap(clkin=>CLKIN,

clkout1k=>XLXN_2,

clkout100=>XLXN_1);

XLXI_9:

control

portmap(ena=>ena,

temp=>XLXN_9);

endBEHAVIORAL;

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- EDA 数字 跑表

冰点文库所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰点文库所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《篮球行进间单手低手投篮》教学设计.docx

《篮球行进间单手低手投篮》教学设计.docx