基于FPGA的即时通讯工具Word格式文档下载.docx

基于FPGA的即时通讯工具Word格式文档下载.docx

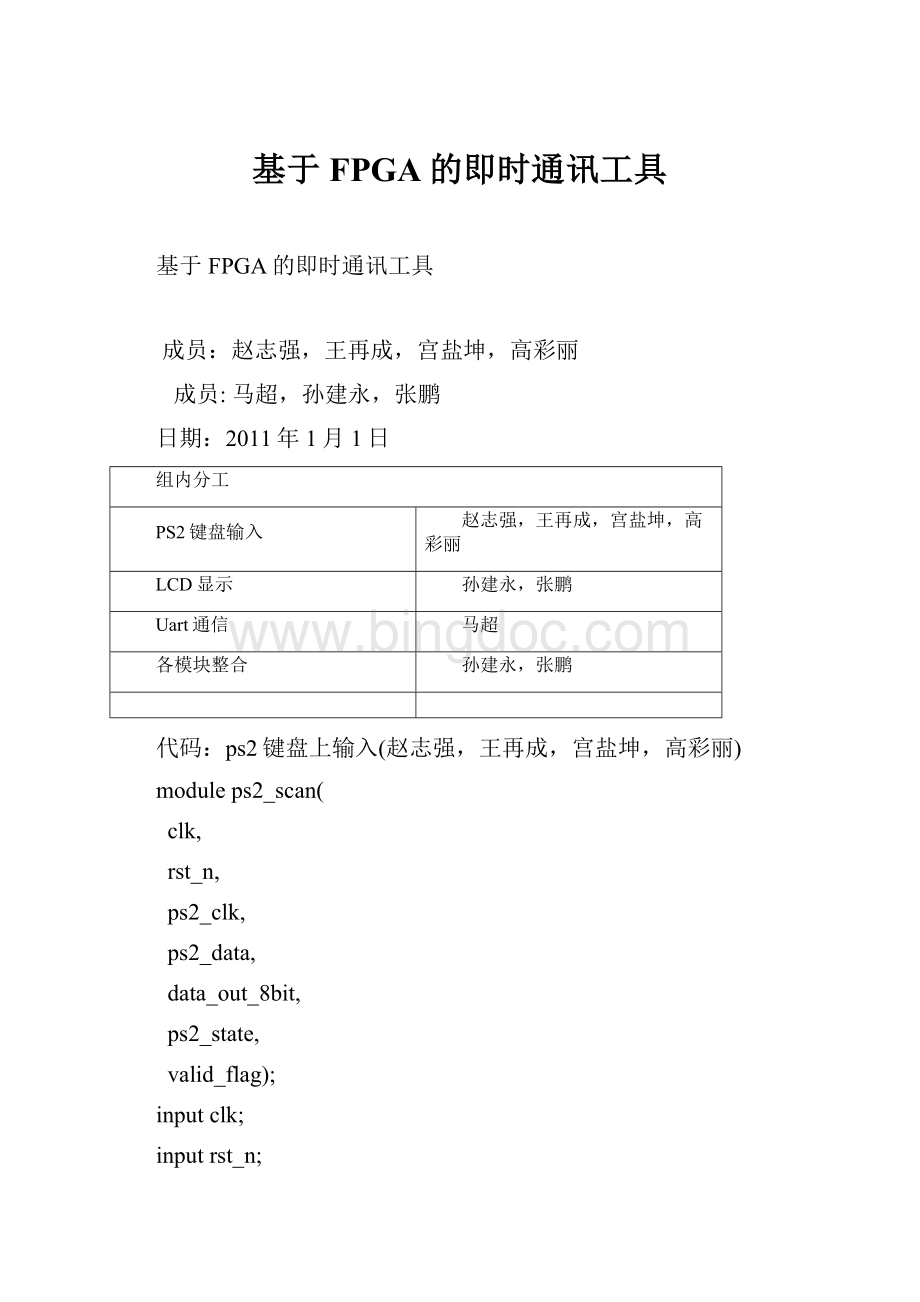

- 文档编号:4783259

- 上传时间:2023-05-04

- 格式:DOCX

- 页数:45

- 大小:22.27KB

基于FPGA的即时通讯工具Word格式文档下载.docx

《基于FPGA的即时通讯工具Word格式文档下载.docx》由会员分享,可在线阅读,更多相关《基于FPGA的即时通讯工具Word格式文档下载.docx(45页珍藏版)》请在冰点文库上搜索。

end

elsebegin

=ps2_clk;

=ps2_clk1;

=ps2_clk2;

wireneg_clkps2;

assignneg_clkps2=~ps2_clk2&

ps2_clk3;

//**************************************************************

regps2_state;

reg[7:

0]ps2_byte_r;

0]temp_data;

reg[3:

0]num;

//当前接收数据寄存?

reg[3:

always@(posedgeclkornegedgerst_n)begin

if(!

rst_n)begin

num<

=4'

d0;

temp_data<

=8'

ps2_state<

elseif(neg_clkps2)begin//ps2k_clk的下降沿接收键盘数据

case(num)

4'

d0:

begin

num<

=num+1'

b1;

ps2_state<

end

d1:

begin

temp_data[0]<

=ps2_data;

//bit0

d2:

temp_data[1]<

//bit1

end

d3:

temp_data[2]<

//bit2

d4:

temp_data[3]<

//bit3

d5:

temp_data[4]<

//bit4

d6:

temp_data[5]<

//bit5

d7:

temp_data[6]<

//bit6

d8:

temp_data[7]<

//bit7

d9:

//奇偶校验位不做处理

4'

d10:

ps2_state<

default:

endcase

end

//******************************************************

regkey_f0;

regreg_valid_flag;

always@(posedgeclkornegedgerst_n)

key_f0<

reg_valid_flag<

endelsebegin

if(num==4'

d10)begin//刚传送完一个字节数据

if(temp_data==8'

hf0)begin

key_f0<

reg_valid_flag<

if(~key_f0)begin

ps2_byte_r<

=temp_data;

//锁存当前键值

reg_valid_flag<

endelsebegin

end

endelsebegin

end

//******************************************************************

0]ps2_asci;

//接SCII码

always@(ps2_byte_r)begin

case(ps2_byte_r)//键值转换为ASCII码

8'

h15:

ps2_asci<

h51;

//Q

h1d:

h57;

//W

h24:

h45;

//E

h2d:

h52;

//R

h2c:

h54;

//T

h35:

h59;

//Y

h3c:

h55;

//U

h43:

h49;

//I

h44:

h4f;

//O

h4d:

h50;

//P

h1c:

h41;

//A

h1b:

h53;

//S

h23:

h44;

//D

h2b:

h46;

//F

h34:

h47;

//G

h33:

h48;

//H

h3b:

h4a;

//J

h42:

h4b;

//K

h4b:

h4c;

//L

h1z:

h5a;

//Z

h22:

h58;

//X

h21:

h43;

//C

h2a:

h56;

//V

h32:

h42;

//B

h31:

h4e;

//N

h3a:

h4d;

//M

8'

h16:

h31;

//1

h1E:

h32;

//2

h26:

h33;

//3

h25:

h34;

//4

h2E:

h35;

//5

h36:

h36;

//6

h3D:

h37;

//7

h3E:

h38;

//8

h46:

h39;

//9

h45:

h30;

//0

h5A:

h0D;

//Enter

default:

h00;

regprev_valid_sig_0;

regprev_valid_sig_1;

always@(posedgeclk)begin

prev_valid_sig_0<

=reg_valid_flag;

prev_valid_sig_1<

=prev_valid_sig_0;

regvalid_flag;

//assignvalid_flag=prev_valid_sig_0&

~prev_valid_sig_1;

if(valid_flag==1'

b1)begin

valid_flag<

endelse

=prev_valid_sig_0&

assigndata_out_8bit=ps2_asci;

endmodule

LCD显示(孙建永,张鹏):

modulelcd(sf_d,

lcd_e,

lcd_rs,

lcd_rw,

rst,

clk,

state,

idle_h,

if_write,

data_input_8bit);

inputrst;

inputclk;

inputif_write;

input[7:

0]data_input_8bit;

outputidle_h;

outputlcd_e;

outputlcd_rs;

outputlcd_rw;

output[3:

0]sf_d;

output[5:

0]state;

reglcd_e;

reglcd_rs;

reglcd_rw;

reg[3:

regidle_h;

parameter

data_stable_wait=2,

lcd_e_h_wait=12,

inter_wait=50,

sta_between_wait=2000,

after_init_wait=2000,

after_cln_dis_wait=92000,

sta_begin_wait=750000,

sta_init_1_wait=205000,

sta_init_2_wait=5000,

sta_init_3_wait=2000,

sta_init_4_wait=2000;

sta_begin=6'

b00_0000,

sta_init_1_1=6'

b00_0001,

sta_init_1_begin_lcd_e_h_wait=6'

b00_0010,

sta_init_1_end=6'

b00_0011,

sta_init_2_begin=6'

b00_0100,

sta_init_2_end=6'

b00_0101,

sta_init_3_begin=6'

b00_0110,

sta_init_3_end=6'

b00_0111,

sta_init_4_begin=6'

b00_1000,

sta_init_4_lcd_e_h_wait=6'

b00_1001,

sta_after_init_4_wait=6'

b00_1010,

sta_function_set_1=6'

b00_1011,

sta_function_set_1_lcd_e_h_wait=6'

b00_1100,

sta_function_set_inter_wait=6'

b00_1101,

sta_function_set_2=6'

b00_1110,

sta_function_set_2_lcd_e_h_wait=6'

b00_1111,

sta_after_function_set_wait=6'

b01_0000,

sta_entry_mode_set_1=6'

b01_0001,

sta_entry_mode_set_1_lcd_e_h_wait=6'

b01_0010,

sta_entry_mode_set_inter_wait=6'

b01_0011,

sta_entry_mode_set_2=6'

b01_0100,

sta_entry_mode_set_2_lcd_e_h_wait=6'

b01_0101,

sta_after_entry_mode_set_wait=6'

b01_0110,

sta_dis_on_off_1=6'

b01_0111,

sta_dis_on_off_1_lcd_e_h_wait=6'

b01_1000,

sta_dis_on_off_inter_wait=6'

b01_1001,

sta_dis_on_off_2=6'

b01_1010,

sta_dis_on_off_lcd_e_h_wait=6'

b01_1011,

sta_after_dis_on_off=6'

b01_1100,

sta_cln_dis_1=6'

b01_1101,

sta_cln_dis_1_lcd_e_h_wait=6'

b01_1110,

sta_cln_dis_inter_wait=6'

b01_1111,

sta_cln_dis_2=6'

b10_0000,

sta_cln_dis_2_lcd_e_h_wait=6'

b10_0001,

sta_after_cln_dis_wait=6'

b10_0010,

sta_write_addr_1=6'

b10_0011,

sta_write_addr_1_lcd_e_h_wait=6'

b10_0100,

sta_write_addr_inter_wait=6'

b10_0101,

sta_write_addr_2=6'

b10_0110,

sta_write_addr_2_lcd_e_h_wait=6'

b10_0111,

sta_after_write_addr=6'

b10_1000,

sta_write_data_1=6'

b10_1001,

sta_write_data_1_lcd_e_h_wait=6'

b10_1010,

sta_write_data_inter_wait=6'

b10_1011,

sta_write_data_2=6'

b10_1100,

sta_write_data_2_lcd_e_h_wait=6'

b10_1101,

sta_write_idle=6'

b10_1110,

sta_write_begin=6'

b10_1111,

sta_write_end_wait=6'

b11_0000,

sta_detect_data=6'

b11_0001;

SET_HIGH_ADDR=8'

b1000_0000,

SET_LOW_ADDR=8'

b1100_0000,

CLN=8'

b1111_1100;

reg[5:

reg[19:

0]cnt;

reg[7:

0]data_write_8bit;

lcd_rw<

always@(posedgeclkornegedgerst)begin

if(rst==1'

b0)begin

state<

=sta_begin;

lcd_rs<

cnt<

=0;

idle_h<

case(state)

sta_begin:

begin

if(cnt==sta_begin_wait)begin

cnt<

state<

=sta_function_set_1;

idle_h<

endelsecnt<

=cnt+1;

sta_function_set_1:

if(cnt==data_stable_wait)begin

lcd_e<

=sta_function_set_1_lcd_e_h_wait;

endelsebegin

cnt<

sf_d<

b0010;

lcd_rs<

end

sta_function_set_1_lcd_e_h_wait:

if(cnt==lcd_e_h_wait)begin

=sta_function_set_inter_wait;

sta_function_set_inter_wait:

if(cnt==inter_wait)begin

=sta_function_set_2;

sta_function_set_2:

=sta_function_set_2_lcd_e_h_wait;

endelsebegin

b1000;

sta_function_set_2_lcd_e_h_wait:

=sta_after_function_set_wait;

sta_after_function_set_wait:

if(cnt==sta_between_wait)begin

=sta_entry_mode_set_1;

sta_entry_mode_set_1:

state<

=sta_entry_mode_set_1_lcd_e_h_wait;

lcd_e<

sf_d<

b0000;

sta_entry_mode_set_1_lcd_e_h_wait:

=sta_entry_mode_set_inter_wait;

sta_entry_mode_set_inter_wait:

=sta_entry_mode_set_2;

sta_entry_mode_set_2:

=sta_entry_mode_set_2_lcd_e_h_wait;

b0110;

end

sta_entry_mode_set_2_lcd_e_h_wait:

if(cnt==lcd_e

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 基于 FPGA 即时通讯 工具

冰点文库所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰点文库所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

整编新型生态农业旅游休闲农庄项目发展建设市场研究报告.docx

整编新型生态农业旅游休闲农庄项目发展建设市场研究报告.docx