多周期MPIS指令集设计Word格式.docx

多周期MPIS指令集设计Word格式.docx

- 文档编号:6425376

- 上传时间:2023-05-06

- 格式:DOCX

- 页数:91

- 大小:574.63KB

多周期MPIS指令集设计Word格式.docx

《多周期MPIS指令集设计Word格式.docx》由会员分享,可在线阅读,更多相关《多周期MPIS指令集设计Word格式.docx(91页珍藏版)》请在冰点文库上搜索。

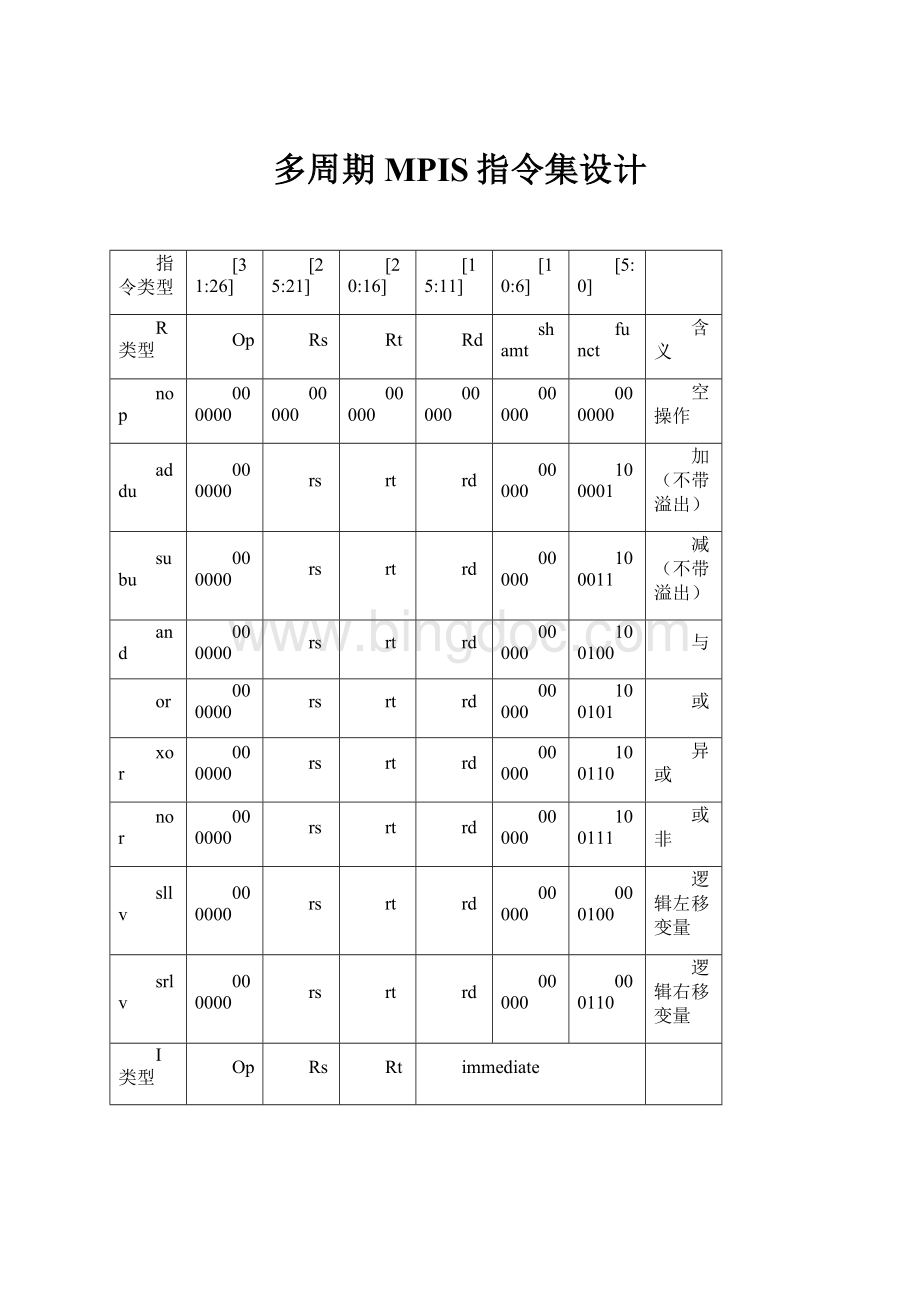

xor

100110

异或

nor

100111

或非

sllv

000100

逻辑左移变量

srlv

000110

逻辑右移变量

I类型

immediate

bltz

000001

Immediate

小于0转移

beq

相等转移

bne

000101

不相等转移

addi

001000

加立即数

andi

001100

与立即数

ori

001101

或立即数

lw

取字

sw

101011

存字

J类型

Address

j

000010

address

无条件跳转

综述:

本设计选用了如下指令,基于此设计出了单周期MIPS处理器,并在单周期的基础上添加了5级流水线设计出了带五级流水线的MIPS处理器。

第一部分单周期MIPS处理器

一、代码

----------------------------------------------------------------------------------

--ModuleName:

top_mips-Behavioral顶层模块

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_ARITH.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

entitytop_mipsis

port(reset:

instd_logic;

clk:

ov:

outstd_logic);

endtop_mips;

architectureBehavioraloftop_mipsis

signals_pc:

std_logic_vector(31downto0);

---pc输入

signals_pc_i:

---pc输出

signals_command:

---指令

signals_add1_pc:

---pc+1值

signals_shift:

std_logic_vector(27downto0);

--指令低26位左移2位后值

signals_jump_pc:

--绝对跳转

signals_regdst:

std_logic;

----控制信号

signals_jump:

std_logic;

signals_branch:

signals_memread:

signals_memtoreg:

signals_aluop:

std_logic_vector(3downto0);

signals_memwrite:

signals_alusrc:

signals_regwrite:

signals_opa:

----ALU操作数

signals_opb:

signals_reg_data:

--寄存器读出的第二个数据

signals_imm_data:

---低16位符号扩展后

signals_zero:

signals_alu_result:

signals_branch_pc:

----条件跳转

signals_1orbranch:

signals_ram_data:

signals_wr_data:

signals_mux:

signals_alu_ctrl:

std_logic_vector(3downto0);

signals_aimreg_addr:

std_logic_vector(4downto0);

写寄存器堆的地址

componentpcis---pc指针模块

pc_i:

instd_logic_vector(31downto0);

pc_o:

outstd_logic_vector(31downto0));

endcomponent;

componentmemoryis---指令存储器

mem_adr:

mem_out:

outstd_logic_vector(31downto0));

componentreg_32bit_arrayis---寄存器堆

wr_en:

addr_wr:

instd_logic_vector(4downto0);

addr1_rd:

addr2_rd:

reg_data_i:

reg_data1_o:

outstd_logic_vector(31downto0);

reg_data2_o:

componentramis---数据存储器

port(reset:

instd_logic;

clk:

rd_en:

wr_en:

addr:

instd_logic_vector(5downto0);

data_i:

data_o:

componentfsmis----指令译码器

port(

command:

instd_logic_vector(5downto0);

regdst:

outstd_logic;

jump:

outstd_logic;

branch:

memread:

memtoreg:

aluop:

outstd_logic_vector(3downto0);

memwrite:

alusrc:

regwrite:

outstd_logic);

componentALU_ctrlis----ALU控制单元

port(

funct_i:

aluop_i:

instd_logic_vector(3downto0);

alu_ctrl_o:

outstd_logic_vector(3downto0));

componentaluis----ALU

op_a,op_b:

alu_ctrl_i:

zero:

result:

componentaddis---加法器

port(

result:

ov:

outstd_logic);

begin

s_shift<

=s_command(25downto0)&

"

00"

;

---左移2位

s_add1_pc<

=s_pc+1;

---pc+1

s_jump_pc<

=s_add1_pc(31downto28)&

s_shift;

---无条件跳转地址

s_mux<

=s_branchands_zero;

s_aimreg_addr<

=s_command(20downto16)whens_regdst='

0'

else

s_command(15downto11);

s_opb<

=s_reg_datawhens_alusrc='

s_imm_data;

s_1orbranch<

=s_add1_pcwhens_mux='

s_branch_pc;

s_pc_i<

=s_1orbranchwhens_jump='

s_jump_pc;

s_wr_data<

=s_alu_resultwhens_memtoreg='

s_ram_data;

---expand

s_imm_data<

=s_command(15)&

x"

0000"

&

s_command(14downto0);

mips_pc:

pcportmap(reset=>

reset,

clk=>

clk,

pc_i=>

s_pc_i,

pc_o=>

s_pc);

mips_memory:

memoryportmap(reset=>

mem_adr=>

s_pc,

mem_out=>

s_command);

mips_regs:

reg_32bit_arrayportmap(

reset=>

clk=>

wr_en=>

s_regwrite,

addr_wr=>

s_aimreg_addr,

addr1_rd=>

s_command(25downto21),

addr2_rd=>

s_command(20downto16),

reg_data_i=>

s_wr_data,

reg_data1_o=>

s_opa,

reg_data2_o=>

s_reg_data);

mips_ram:

ramportmap(reset=>

clk=>

wr_en=>

s_memwrite,

rd_en=>

s_memread,

addr=>

s_alu_result(5downto0),

data_i=>

s_reg_data,

data_o=>

s_ram_data);

mips_fsm:

fsmportmap(command=>

s_command(31downto26),

regdst=>

s_regdst,

jump=>

s_jump,

branch=>

s_branch,

memread=>

s_memread,

memtoreg=>

s_memtoreg,

aluop=>

s_aluop,

memwrite=>

alusrc=>

s_alusrc,

regwrite=>

s_regwrite);

mips_aluctrl:

ALU_ctrlportmap(funct_i=>

s_command(5downto0),

aluop_i=>

alu_ctrl_o=>

s_alu_ctrl);

mips_alu:

aluportmap(op_a=>

op_b=>

s_opb,

alu_ctrl_i=>

s_alu_ctrl,

zero=>

s_zero,

result=>

s_alu_result);

mips_add:

addportmap(op_a=>

s_add1_pc,

s_imm_data,

s_branch_pc,

ov=>

ov);

endBehavioral;

pc-Behavioralpc模块

entitypcis

instd_logic_vector(31downto0);

endpc;

architectureBehavioralofpcis

process(clk,reset,pc_i)

begin

ifreset='

1'

then

pc_o<

=x"

00000000"

elsif(clk'

eventandclk='

)then

pc_o<

=pc_i;

endif;

endprocess;

memory-Behavioral程序存储器模块

------------------------------指令存储器64×

32----------------------------------------------------

entitymemoryis

endmemory;

architectureBehavioralofmemoryis

TYPEmem_dataisarray(0to63)ofstd_logic_vector(31downto0);

---指令存储器

signalrom_table:

mem_data;

begin

process(reset,mem_adr,rom_table)

if(reset='

rom_table<

=(---------将指令通过RESET固化进去

"

00000000000000000000000000000000"

---nop

"

00000000001000100000100000100000"

---add

00000000011000100001000000100010"

---sub

00000000100001010001100000100100"

---and

00000000110001110010000000100101"

---or

00000001000010010010100000100110"

---xor

00000001010010110011000000100111"

---nor

00000001100011010011100000000100"

---sllv

00000001110011110100000000000110"

---srlv

00000111111000000000000000000010"

---bltz

00010010001011110000000000000010"

---beq

00010110010100110000000000000010"

---ben

00000110000000000000000000000010"

00010010001100010000000000000010"

00010111111000000000000000000010"

00100010011111100000000011111111"

---addi

00110010100111010000000000011001"

---andi

00110110110111000000000000011000"

---ori

10001100000110110000000000001111"

---lw

10101100000101110000000000011111"

---sw

00001000000000000000000000011101"

---j

000000000000000000000

- 配套讲稿:

如PPT文件的首页显示word图标,表示该PPT已包含配套word讲稿。双击word图标可打开word文档。

- 特殊限制:

部分文档作品中含有的国旗、国徽等图片,仅作为作品整体效果示例展示,禁止商用。设计者仅对作品中独创性部分享有著作权。

- 关 键 词:

- 周期 MPIS 指令 设计

冰点文库所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

冰点文库所有资源均是用户自行上传分享,仅供网友学习交流,未经上传用户书面授权,请勿作他用。

《安全在我心中生命在我手中》主题班会教案.docx

《安全在我心中生命在我手中》主题班会教案.docx